### Design of CMOS Millimeter-Wave and Terahertz Integrated Circuits with Metamaterials

### Hao Yu • Yang Shang

Design of CMOS Millimeter-Wave and Terahertz Integrated Circuits with Metamaterials

### Design of CMOS Millimeter-Wave and Terahertz Integrated Circuits with Metamaterials

Hao Yu Yang Shang

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2016 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20150806

International Standard Book Number-13: 978-1-4822-3816-7 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

### Contents

| Li       | st of  | Figures                                           | ci |

|----------|--------|---------------------------------------------------|----|

| Li       | st of  | Tables                                            | v  |

| Pı       | reface | e                                                 | ii |

| A        | cknov  | wledgments xxx                                    | ci |

| SI       | ЕСТ    | TION I: FUNDAMENTALS                              | 1  |

| 1        | Intr   |                                                   | 3  |

|          | 1.1    | Overview of Terahertz Technology                  | 3  |

|          |        | 1.1.1 Terahertz Applications                      | 3  |

|          |        | 1.1.2 Optics-Based Terahertz System               | 6  |

|          | 1.2    | CMOS THz Electronics                              | 8  |

|          | 1.3    | CMOS THz Applications                             | 9  |

|          |        | 1.3.1 THz CMOS Imaging                            | 9  |

|          |        | 1.3.2 THz CMOS Communication                      | 0  |

| <b>2</b> | CM     | OS Metamaterial Devices                           | 5  |

|          | 2.1    | Introduction                                      | 5  |

|          | 2.2    | Non-Resonant-Type Metamaterial 1                  | 6  |

|          |        | 2.2.1 Composite Right-/Left-Handed T-Line         | 7  |

|          |        | 2.2.2 Magnetic Plasmon Waveguide                  | 9  |

|          | 2.3    | Resonant-Type Metamaterial                        | 1  |

|          |        |                                                   | 2  |

|          |        | 2.3.2 T-Line Loaded with Complementary Split Ring |    |

|          |        | Resonator                                         | 3  |

|          | 2.4    | CMOS Coherent THz Electronics by Metamaterial 3   | 4  |

|          |        | 2.4.1 Coherent Source                             | 4  |

|              |                          | 2.4.2                                                                                                           | Coherent Transmission                           | 36                                                                   |

|--------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|

|              |                          | 2.4.3                                                                                                           | Coherent Detection                              | 37                                                                   |

|              |                          | 2.4.4                                                                                                           | Transceiver Architecture                        | 38                                                                   |

| 3            | $\mathbf{C}\mathbf{M}$   | OS TH                                                                                                           | Iz Modeling                                     | 39                                                                   |

|              | 3.1                      | Introd                                                                                                          | uction                                          | 39                                                                   |

|              | 3.2                      | Fractio                                                                                                         | onal-Order T-Line Model                         | 41                                                                   |

|              |                          | 3.2.1                                                                                                           | Fractional Calculus                             | 41                                                                   |

|              |                          | 3.2.2                                                                                                           | Fractional-Order Capacitance and Inductance     | 42                                                                   |

|              |                          | 3.2.3                                                                                                           | Fractional-Order T-Line Model                   | 42                                                                   |

|              |                          | 3.2.4                                                                                                           | Fractional-Order CRLH T-Line Model              | 44                                                                   |

|              | 3.3                      | Model                                                                                                           | Extraction and Causality Analysis               | 46                                                                   |

|              |                          | 3.3.1                                                                                                           | Fractional-Order Model Extraction               | 46                                                                   |

|              |                          | 3.3.2                                                                                                           | Causal LTI System and Causality Enforcement     | 47                                                                   |

|              |                          | 3.3.3                                                                                                           | Causality of T-Line Model                       | 49                                                                   |

|              | 3.4                      |                                                                                                                 | yping and Measurement                           | 50                                                                   |

|              |                          | 3.4.1                                                                                                           | T-Line Fractional-Order Model Verification      | 50                                                                   |

|              |                          | 3.4.2                                                                                                           | CRLH T-Line Fractional-Order Model Verification | 53                                                                   |

|              |                          | 3.4.3                                                                                                           | Causality Verification and Comparison           | 55                                                                   |

|              | 3.5                      | Conclu                                                                                                          | v 1                                             | 61                                                                   |

|              |                          |                                                                                                                 |                                                 |                                                                      |

|              |                          |                                                                                                                 |                                                 |                                                                      |

| $\mathbf{S}$ | ЕСТ                      | ION                                                                                                             | II: CMOS THZ SIGNAL GENERATION                  | 63                                                                   |

| $\mathbf{S}$ |                          |                                                                                                                 | II: CMOS THZ SIGNAL GENERATION                  | 63<br>65                                                             |

|              |                          | illator                                                                                                         |                                                 |                                                                      |

|              | Osc                      | <b>illator</b><br>Introd                                                                                        | uction                                          | 65                                                                   |

|              | <b>Osc</b><br>4.1        | <b>illator</b><br>Introd                                                                                        |                                                 | <b>65</b><br>65                                                      |

|              | <b>Osc</b><br>4.1        | <b>illator</b><br>Introd<br>Freque                                                                              | uction                                          | <b>65</b><br>65<br>67                                                |

|              | <b>Osc</b><br>4.1        | <b>illator</b><br>Introd<br>Freque<br>4.2.1                                                                     | uction                                          | <b>65</b><br>65<br>67                                                |

|              | <b>Osc</b><br>4.1        | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2                                                                   | uction                                          | <b>65</b><br>65<br>67<br>67                                          |

|              | Osc<br>4.1<br>4.2        | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2                                                                   | uction                                          | <b>65</b><br>65<br>67<br>67<br>71                                    |

|              | Osc<br>4.1<br>4.2        | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque                                                         | uction                                          | <b>65</b><br>65<br>67<br>67<br>71<br>80                              |

|              | Osc<br>4.1<br>4.2        | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1                                                | uction                                          | <b>65</b><br>65<br>67<br>67<br>71<br>80                              |

|              | Osc<br>4.1<br>4.2        | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2                                       | uction                                          | <b>65</b><br>65<br>67<br>67<br>71<br>80<br>80                        |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2                                       | uction                                          | 65<br>65<br>67<br>67<br>71<br>80<br>80<br>80                         |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2<br>Circuit                            | uction                                          | 65<br>65<br>67<br>67<br>71<br>80<br>80<br>80                         |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2<br>Circuit                            | uction                                          | <b>65</b><br>65<br>67<br>67<br>71<br>80<br>80<br>80<br>82<br>84      |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2<br>Circuit<br>4.4.1                   | uction                                          | <b>65</b><br>65<br>67<br>67<br>71<br>80<br>80<br>80<br>82<br>84      |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2<br>Circuit<br>4.4.1                   | uction                                          | 65<br>65<br>67<br>67<br>71<br>80<br>80<br>80<br>82<br>84<br>84       |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2<br>Circuit<br>4.4.1<br>4.4.2          | uction                                          | 65<br>65<br>67<br>67<br>71<br>80<br>80<br>80<br>82<br>84<br>84       |

|              | Osc<br>4.1<br>4.2<br>4.3 | illator<br>Introd<br>Freque<br>4.2.1<br>4.2.2<br>Freque<br>4.3.1<br>4.3.2<br>Circuit<br>4.4.1<br>4.4.2<br>4.4.3 | uction                                          | 65<br>65<br>67<br>67<br>71<br>80<br>80<br>80<br>82<br>84<br>84<br>91 |

| <b>5</b> | Cοι               | pled Oscillator Network                                                  | 105          |

|----------|-------------------|--------------------------------------------------------------------------|--------------|

|          | 5.1               | Introduction                                                             | 105          |

|          | 5.2               | In-Phase Signal Generation by MPW                                        | 107          |

|          | 5.3               | Circuit Prototyping and Measurement                                      | 109          |

|          |                   | 5.3.1 60 GHz CON Signal Source                                           | 109          |

|          |                   | 5.3.2 140 GHz CON Signal Source                                          | 116          |

|          |                   | 5.3.3 280 GHz CON Signal Source                                          | 125          |

|          | 5.4               | Conclusion                                                               | 133          |

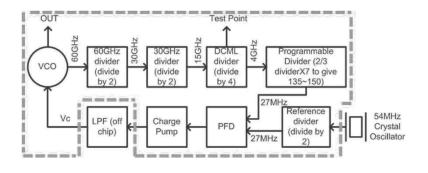

| 6        | Pha               | se-Locked Loop                                                           | 135          |

|          | 6.1               | Introduction                                                             | 135          |

|          | 6.2               | 60-GHz PLL Design                                                        | 137          |

|          | 6.3               | Circuit Prototyping and Simulation                                       | 140          |

|          |                   | 6.3.1 Divider Measurement Results                                        | 140          |

|          |                   | 6.3.2 PLL Simulation Results                                             | 142          |

| SI       | ЕСТ               | TION III: CMOS THZ SIGNAL AMPLIFI-                                       |              |

| 51       |                   | TION AND TRANSMISSION                                                    | 145          |

| 7        | Dor               | ver Combiner                                                             | 147          |

| 1        | <b>FOV</b><br>7.1 | Introduction                                                             | 147          |

|          | $7.1 \\ 7.2$      | In-Phase Signal Transmission by CRLH Zero-Phase-Shifter                  | 147          |

|          | $7.2 \\ 7.3$      | PA Design with Power Combining Network                                   | $140 \\ 150$ |

|          | 1.5               | 7.3.1 SEDFDA-Based PA Design                                             | $150 \\ 150$ |

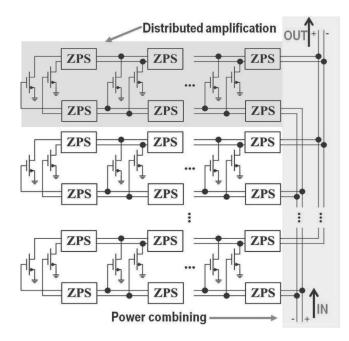

|          |                   | 7.3.2 ZPS-Based 2D Distributed Power Combining for PA                    | 150          |

|          |                   | 7.3.3 Stabilization Techniques                                           | 167          |

|          |                   | 7.3.3       Stabilization Techniques         7.3.4       Digital Control | 162          |

|          | 7.4               | Circuit Prototyping and Measurement                                      | 173          |

|          | 1.4               | 7.4.1 60 GHz PA Design with Single-Ended $2 \times 2$ Power              | 175          |

|          |                   | Combining                                                                | 173          |

|          |                   | 7.4.2 60 GHw PA Design with Differential $2 \times 4$ Power              |              |

|          |                   | Combining                                                                | 178          |

|          |                   | 7.4.3 60 GHz PA Prototype with Differential $4 \times 4$ Power           |              |

|          |                   | Combining and Digital Control                                            | 181          |

|          | 7.5               | Conclusion                                                               | 195          |

| 8        | Ant               | enna                                                                     | 197          |

|          | 8.1               | Introduction                                                             | 197          |

|          | 8.2               | CRLH T-Line-Based Leaky Wave Antenna                                     | 198          |

|          | 8.3               | Circularly Polarized SIW Antenna                                         | 199          |

|          | 8.4               | Circuit Prototyping and Measurement                                      | 202          |

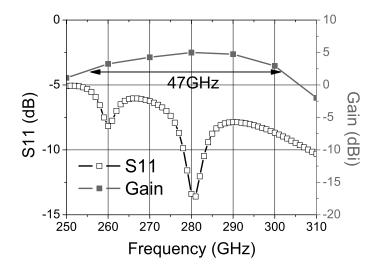

|          |                   | 8.4.1 280-GHz LWA                                                        | 202          |

|          |                   | 8.4.2 280-GHz SIW                                                        | 206          |

|          | 8.5               | Conclusion                                                               | 209          |

### SECTION IV: CMOS THZ SIGNAL DETECTION 211

| 9  | Res  | onator                                              | <b>213</b>   |

|----|------|-----------------------------------------------------|--------------|

|    | 9.1  | Introduction                                        | 213          |

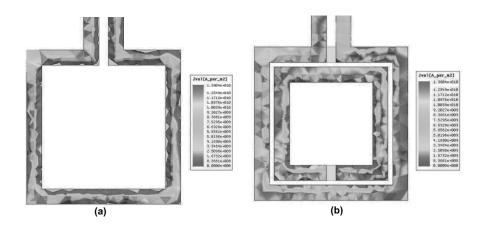

|    | 9.2  | Differential TL-SRR Resonator                       | 214          |

|    |      | 9.2.1 Stacked SRR Layout                            | 214          |

|    |      | 9.2.2 Comparison with Single-Ended TL-SRR Resonator | 215          |

|    |      | 9.2.3 Comparison with Standing-Wave Resonator       | 217          |

|    | 9.3  | Differential TL-CSRR Resonator                      | 218          |

|    | 9.4  | Circuit Prototyping and Measurement                 | 220          |

|    |      | 9.4.1 76-GHz Differential TL-SRR Resonator          | 220          |

|    |      | 9.4.2 96-GHz Differential TL-CSRR Resonator         | 223          |

|    |      | 9.4.3 Measurements                                  | 223          |

|    | 9.5  | Conclusion                                          | 230          |

| 10 | Sup  | er-Regenerative Detection                           | 231          |

| 10 |      | Introduction                                        | 231          |

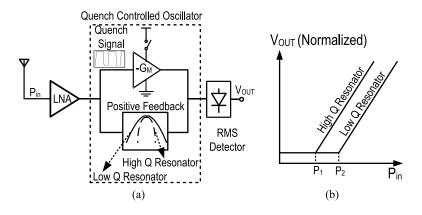

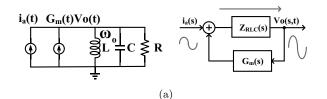

|    |      | Fundamentals of Super-Regenerative Amplification    | $231 \\ 233$ |

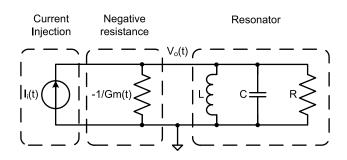

|    | 10.2 | 10.2.1 Equivalent Circuit of SRA                    | 233<br>234   |

|    |      | 10.2.1 Equivalent Circuit of SKA                    |              |

|    |      |                                                     | 235          |

|    | 10.9 | 10.2.3 Sensitivity of SRA                           | 235          |

|    | 10.3 | Super-Regenerative Receiver by SRR/CSRR Resonator   | 236          |

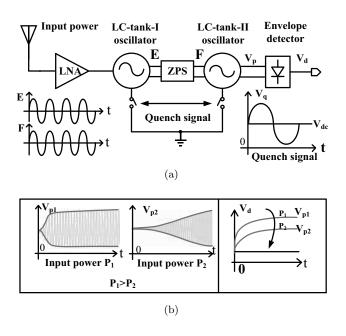

|    |      | 10.3.1 Quench-Controlled Oscillation                | 237          |

|    |      | 10.3.2 SRX Design by TL-CSRR                        | 239          |

|    | 10.4 | 10.3.3 SRX Design by TL-SRR                         | 240          |

|    | 10.4 | Circuit Prototyping and Measurement                 | 244          |

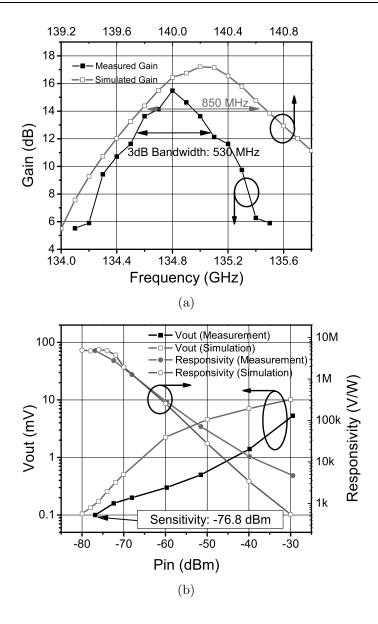

|    |      | 10.4.1 DTL-CSRR-Based SRX at 96 GHz                 | 244          |

|    |      | 10.4.2 DTL-SRR-Based SRX at 135 GHz                 | 246          |

|    |      | 10.4.3 Comparison and Discussion                    | 249          |

|    | 10.5 | Conclusion                                          | 249          |

| 11 | In-F | Phase Detection                                     | <b>251</b>   |

|    | 11.1 | Introduction                                        | 251          |

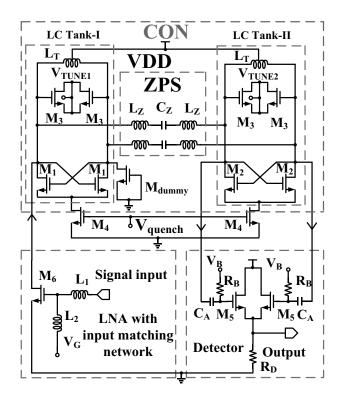

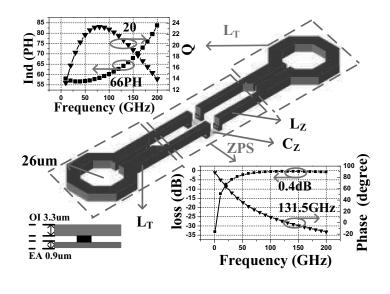

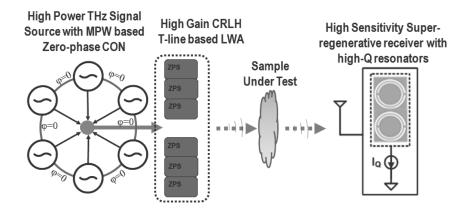

|    | 11.2 | SRX Sensitivity Enhancement by ZPS-Coupled CON      | 251          |

|    | 11.3 | Circuit Prototyping and Measurement                 | 254          |

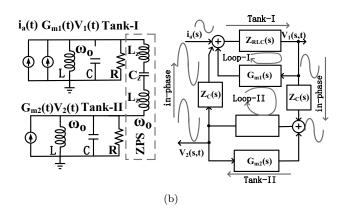

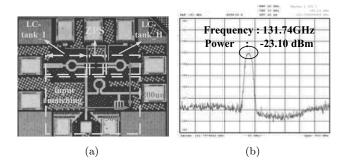

|    |      | 11.3.1 SRX Circuit Design                           | 254          |

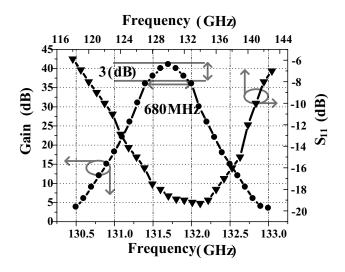

|    |      | 11.3.2 Measurements                                 | 256          |

|    | 11.4 | Conclusion                                          | 258          |

| SF | ECT  | TON V: APPLICATIONS                                 | 259          |

| 12 | СМ   | OS THz Imaging                                      | <b>261</b>   |

|    |      | Introduction                                        | 261          |

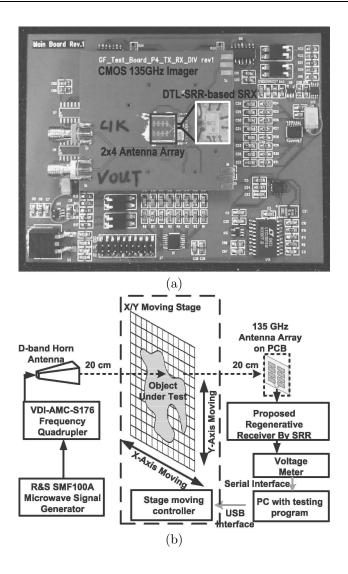

|    | 12.2 | 135-GHz Narrow-Band Imager by DTL-SRR-Based SRX     | 263          |

|    |      | 12.2.1 THz Imaging by SRA Detection                 | 263          |

|    |      |                                                     |              |

|    |      | 12.2.2 Narrow-Band Imaging Results                            | 263 |

|----|------|---------------------------------------------------------------|-----|

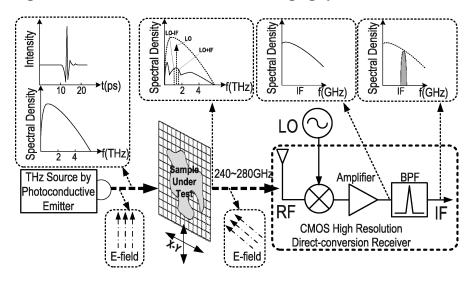

|    | 12.3 | $240 \sim 280$ -GHz Wide-Band Imager with Heterodyne Receiver | 267 |

|    |      | 12.3.1 Architecture and System Specification                  | 268 |

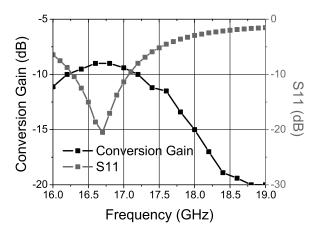

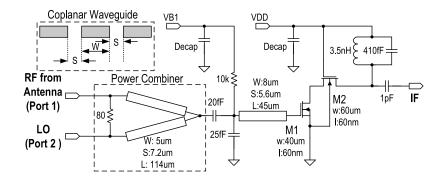

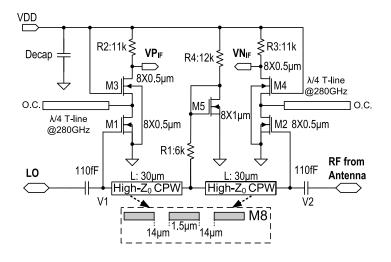

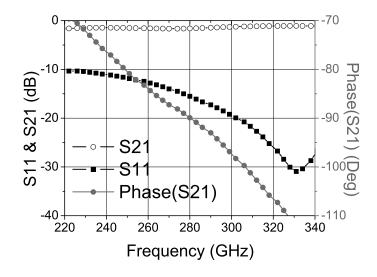

|    |      | 12.3.2 Down-Conversion Mixer                                  | 268 |

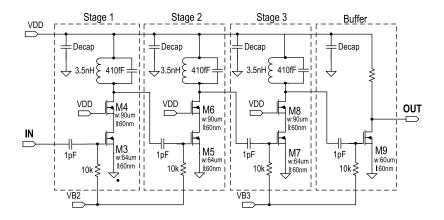

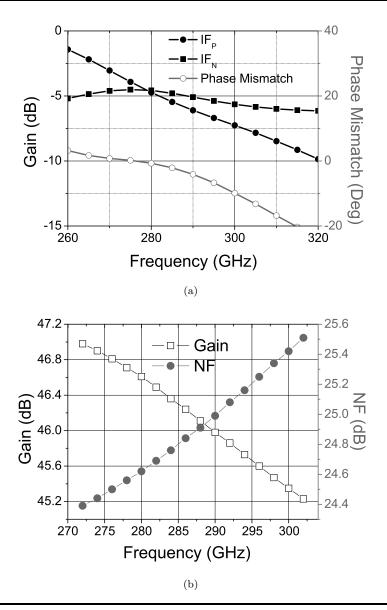

|    |      | 12.3.3 Power Gain Amplifier                                   | 269 |

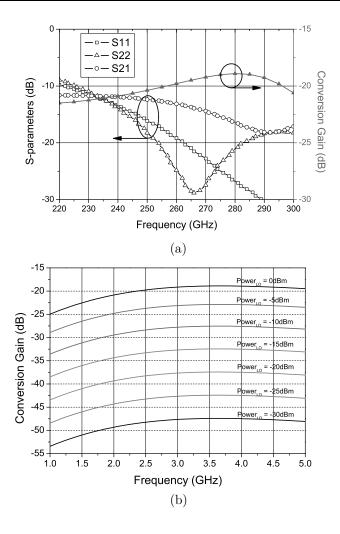

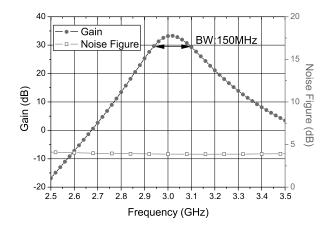

|    |      | 12.3.4 Wide-Band Imaging Results                              | 271 |

|    |      | 12.3.5 Wide-Band THz Imaging                                  | 277 |

|    | 12.4 | 280-GHz Reflective Imaging System                             | 277 |

|    |      | 12.4.1 Differential Down-Conversion Receiver                  | 279 |

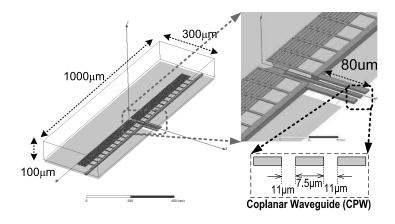

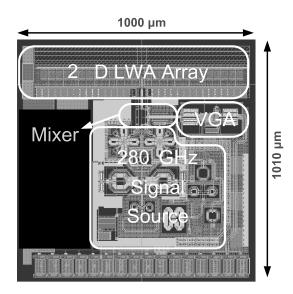

|    |      | 12.4.2 2D On-Chip Leaky Wave Antenna Array                    | 283 |

|    |      | 12.4.3 Transceiver Integration                                | 285 |

|    | 12.5 | Conclusion                                                    | 288 |

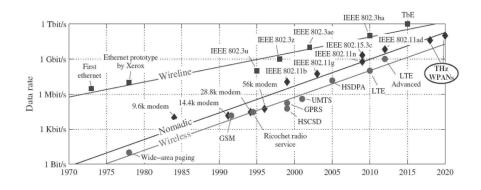

| 13 | CM   | OS THz Wireless Communication                                 | 289 |

|    | 13.1 | Introduction                                                  | 289 |

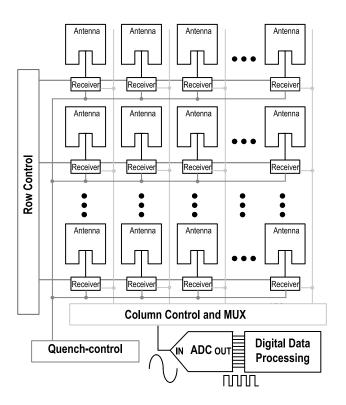

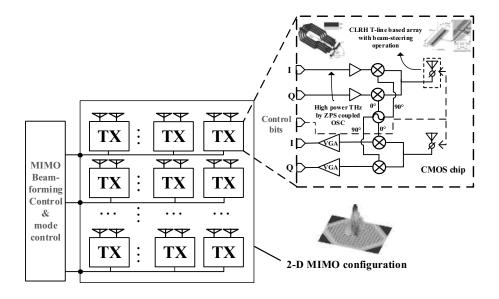

|    | 13.2 | Massive MIMO Transceiver                                      | 292 |

|    | 13.3 | Conclusion                                                    | 294 |

| 14 | CM   | OS THz Wireline Communication                                 | 297 |

|    |      | Introduction                                                  | 297 |

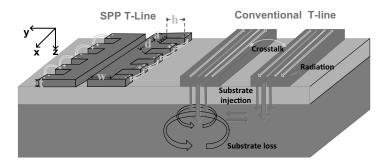

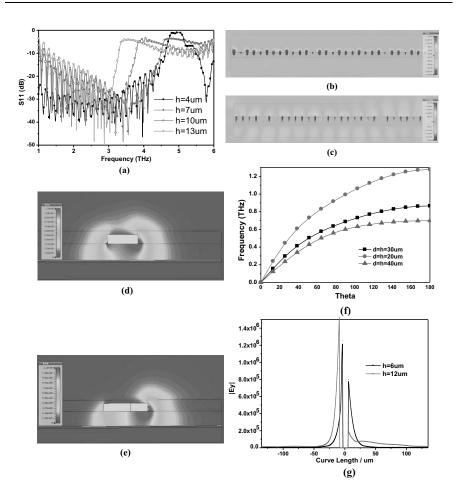

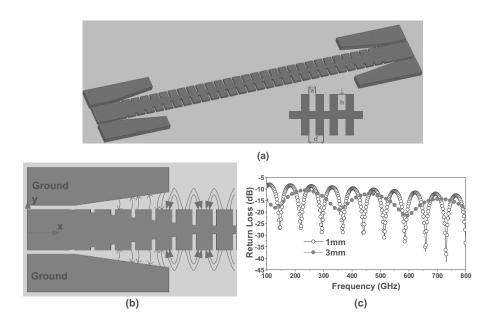

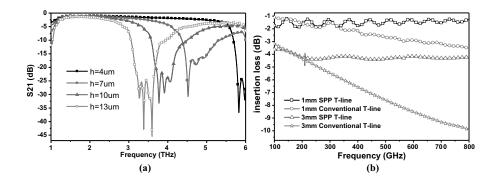

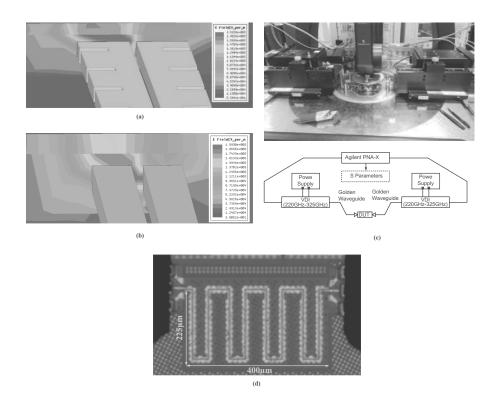

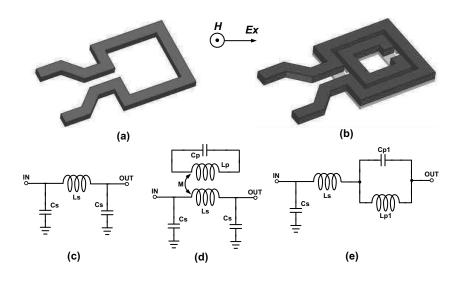

|    | 14.2 | Surface Plasmon Polariton T-Line                              | 299 |

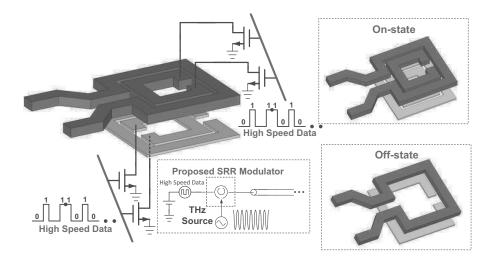

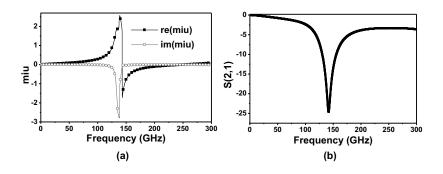

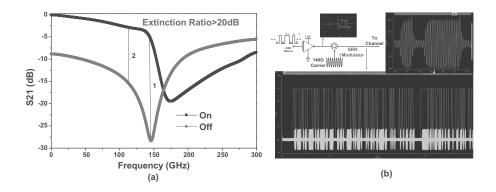

|    | 14.3 | SRR Modulator                                                 | 311 |

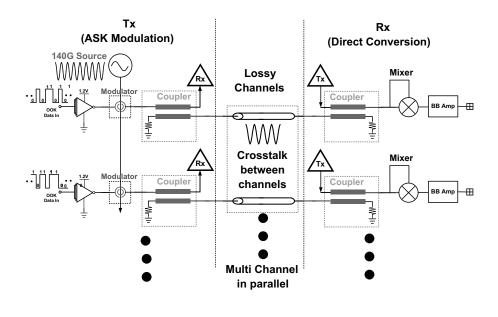

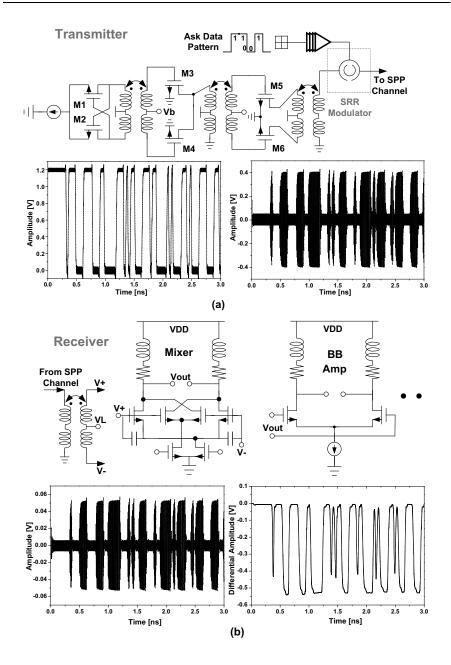

|    |      | Multi-Channel I/O Transceiver                                 | 317 |

|    |      | Conclusion                                                    | 323 |

| Re | fere | nces                                                          | 325 |

# List of Figures

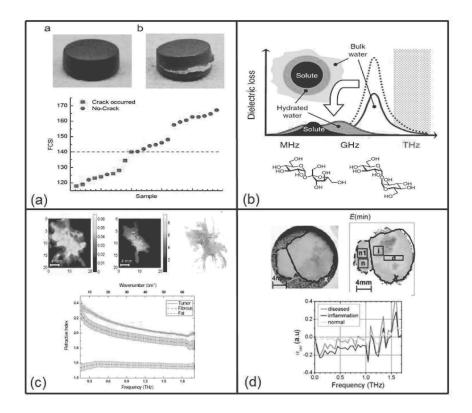

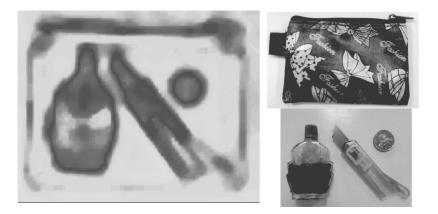

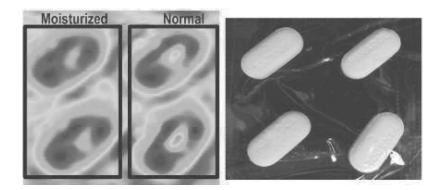

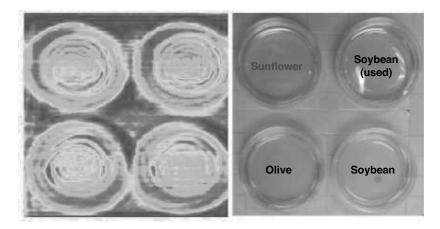

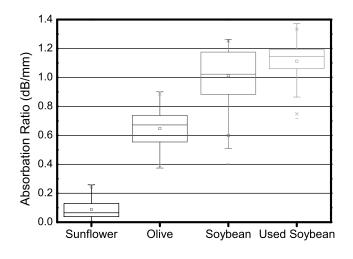

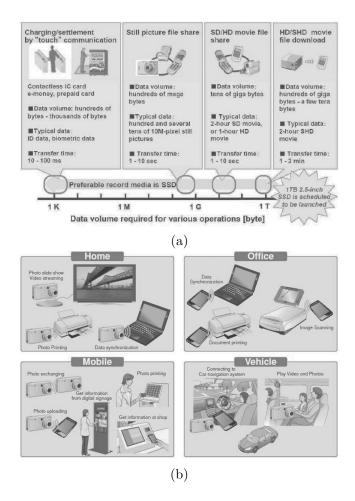

| 1.1  | Application examples of THz spectroscopy and imaging                 | 5  |

|------|----------------------------------------------------------------------|----|

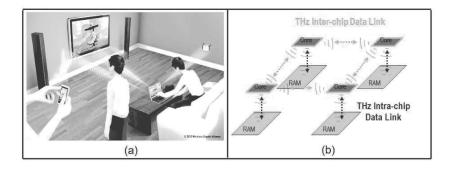

| 1.2  | Application examples of THz communication.                           | 7  |

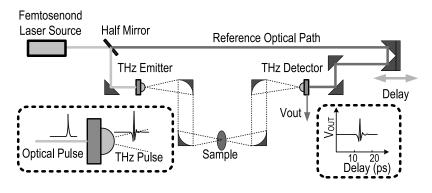

| 1.3  | Schematic of a THz spectroscopy and imaging system by                |    |

|      | electro-optic sampling technique in transmission type                | 7  |

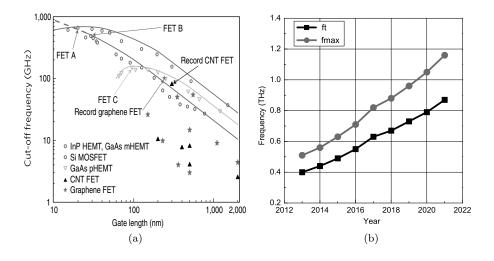

| 1.4  | (a) Comparing cut-off frequencies for different FETs; (b) ITRS       |    |

|      | projected $f_{max}$ and $f_t$ of NMOS transistors                    | 8  |

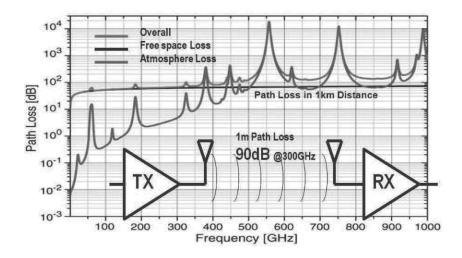

| 1.5  | Design challenges of THz imaging system to overcome the huge         |    |

|      | path                                                                 | 9  |

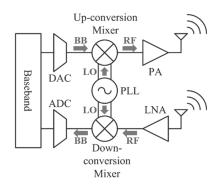

| 1.6  | Simplified block diagram for a 60 GHz CMOS direct-                   |    |

|      | conversion transceiver front end                                     | 11 |

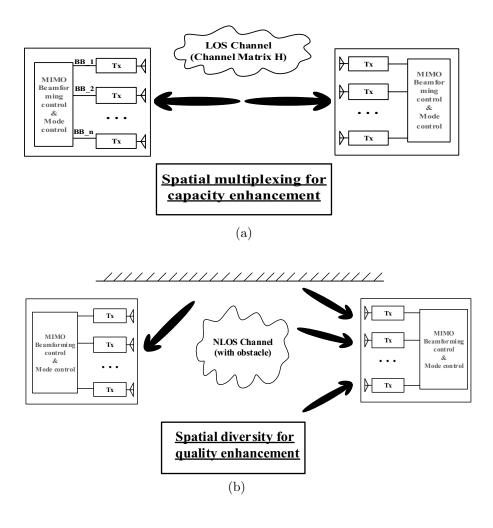

| 1.7  | Two massive MIMO modes proposed for THz wireless link                | 13 |

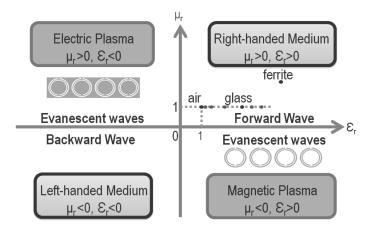

| 2.1  | Definition of metamaterial                                           | 16 |

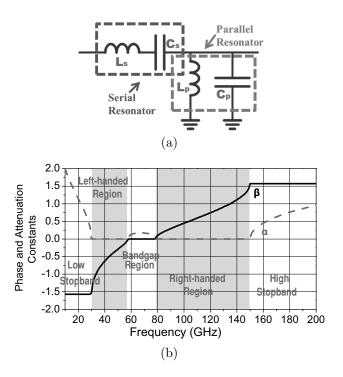

| 2.2  | CRLH T-line: (a) equivalent circuit for T-line unit cell, (b)        |    |

|      | operating regions                                                    | 18 |

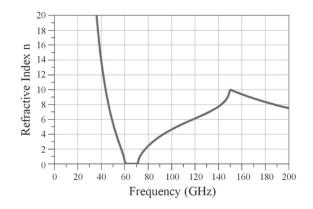

| 2.3  | Refractive index for 2D CRLH metamaterial                            | 20 |

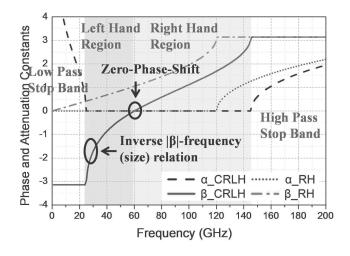

| 2.4  | Dispersion diagram for CRLH T-line in the balanced case with         |    |

|      | comparison of RH T-line                                              | 21 |

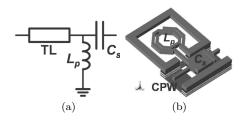

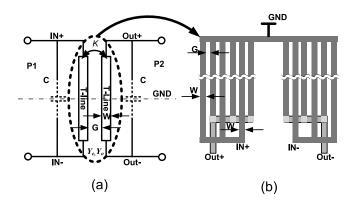

| 2.5  | CRLH T-line-based ZPS unit cell: (a) schematic (b) layout.           | 23 |

| 2.6  | Simulated and measured S parameters for unit cell of CRLH            |    |

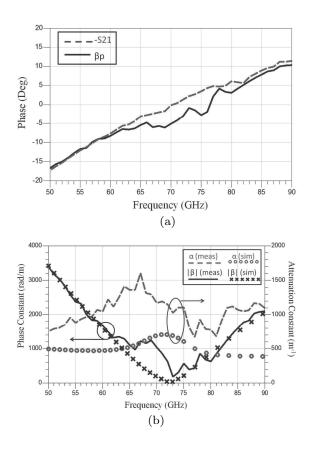

|      | T-line-based ZPS                                                     | 24 |

| 2.7  | Characterization of CRLH T-line unit cell: (a) ZPS perfor-           |    |

|      | mance, (b) propagation constant. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 25 |

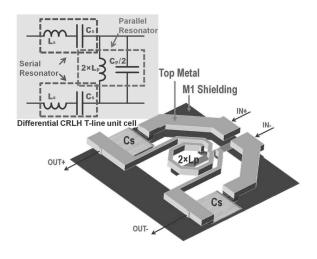

| 2.8  | Equivalent circuit and layout diagrams for one unit cell of          |    |

|      | differential CRLH T-line-based zero-phase shifter                    | 26 |

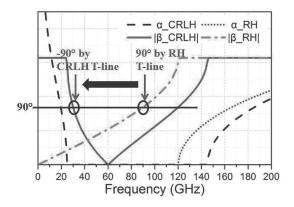

| 2.9  | Compact size for negative-Chase CRLH T-line to achieve the           |    |

|      | same 90° phase-shift compared to traditional RH T-line               | 27 |

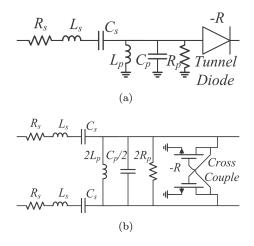

| 2.10 | Traditional active CRLH T-line using tunnel diode or cross-          |    |

|      | coupled transistor to compensate for the propagation loss            | 29 |

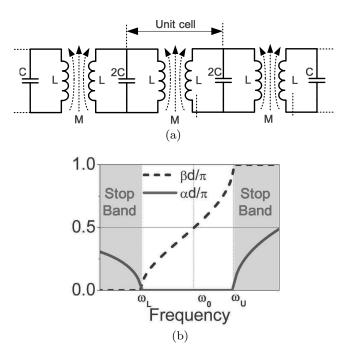

| 2.11 | <ul><li>(a) Equivalent circuit of magnetic plasmon waveguide (MPW);</li><li>(b) dispersion diagram of MPW.</li></ul>                                                | 3(           |

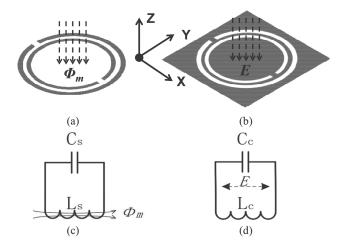

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.12 | Layout topologies of SRR in (a), CSRR in (b), equivalent circuits of SRR in (c), CSRR in (d).                                                                       | 3            |

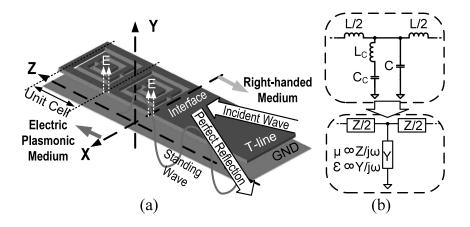

| 2.13 | <ul><li>(a) Standing-wave formed by perfect reflection at DTL-SRR;</li><li>(b) equivalent circuit of DTL-SRR with condition to form perfect reflection.</li></ul>   | 32           |

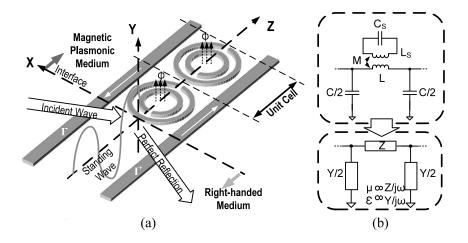

| 2.14 | <ul><li>(a) Standing-wave formed by perfect reflection at DTL-CSRR;</li><li>(b) equivalent circuit of DTL-CSRR with condition to form perfect reflection.</li></ul> | 3            |

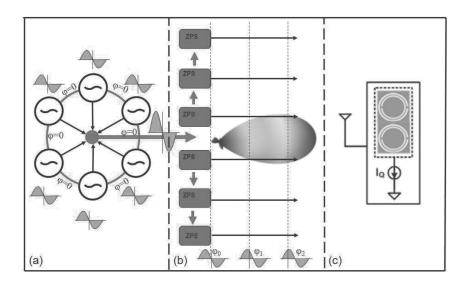

| 2.15 | Metamaterial-based THz transceiver design                                                                                                                           | $3^{\prime}$ |

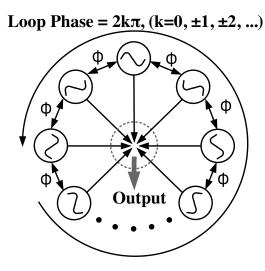

| 2.16 | Closed-loop coupled oscillator network with center combined output.                                                                                                 | 3!           |

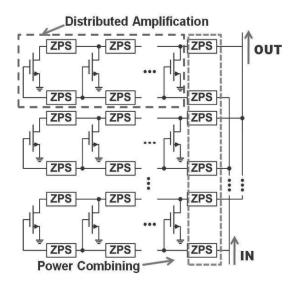

| 2.17 | Single-ended version on proposed SEDFDA PA topology<br>based on 2D distributed power-combining network with the<br>use of CRLH ZPSs                                 | 3'           |

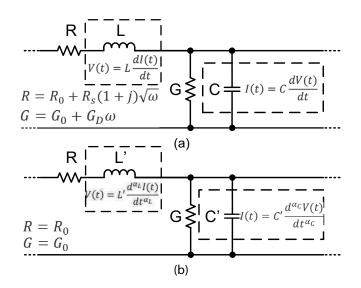

| 3.1  | RLGC unit-cell equivalent circuits of T-line.                                                                                                                       | 4            |

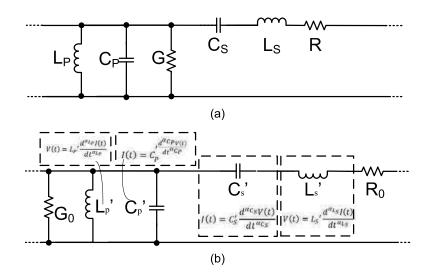

| 3.2  | Equivalent circuits of CRLH unit-cell.                                                                                                                              | 44           |

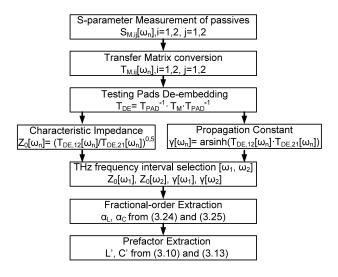

| 3.3  | Fractional-order T-line modeling parameters extraction flow.                                                                                                        | 4'           |

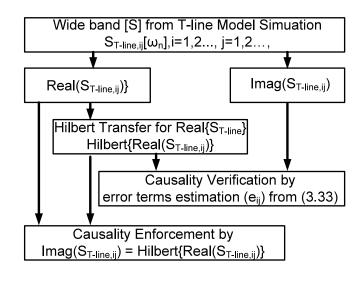

| 3.4  | Causality verification and enforcement flow.                                                                                                                        | 49           |

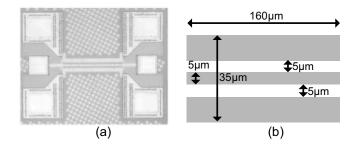

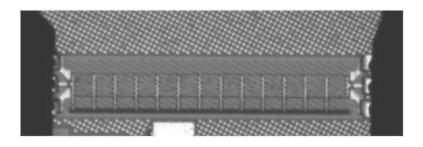

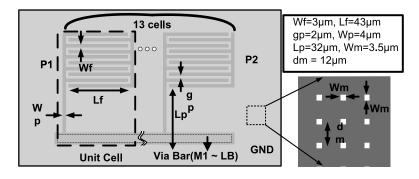

| 3.5  | T-line testing structure: (a) die photo, and (b) detailed dimen-<br>sions.                                                                                          | 5            |

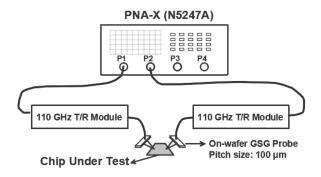

| 3.6  | Measurement setup of on-wafer S-parameter testing up to 110<br>GHz                                                                                                  | 5            |

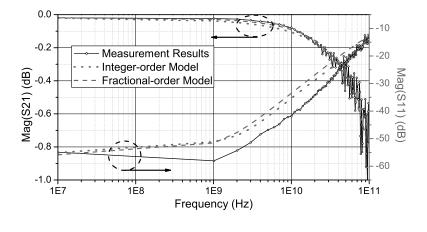

| 3.7  | Verification of fractional-order T-line model with measure-<br>ment results for magnitude of S11 and S21 in dB                                                      | 52           |

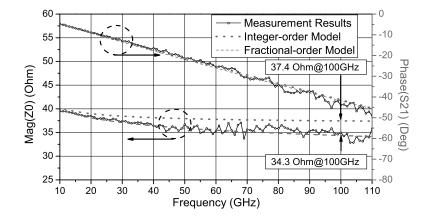

| 3.8  | Verification of fractional-order T-line model with measure-<br>ment results for phase delay of S21 and characteristic                                               |              |

| 3.9  | impedance                                                                                                                                                           | 5            |

| 9 10 | process                                                                                                                                                             | 54<br>5      |

| 3.10 | Dimension of each unit-cell and layer configurations of LWA.<br>Measurement setup of on-wafer S-parameter testing from 220                                          | $5_4$        |

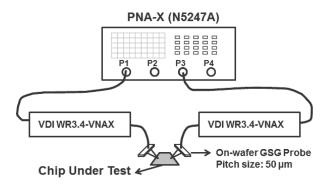

| 3.11 | GHz to 325 GHz.                                                                                                                                                     | E.           |

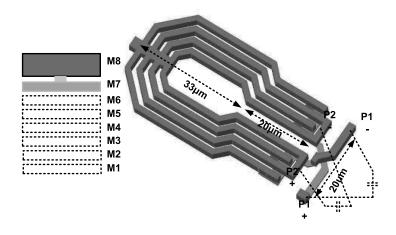

| 9 10 |                                                                                                                                                                     | 5            |

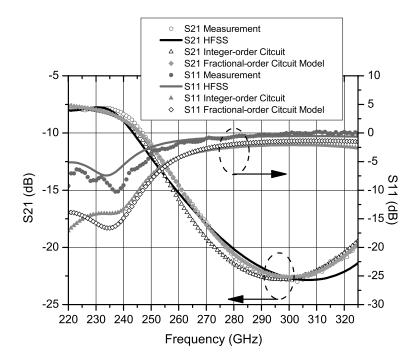

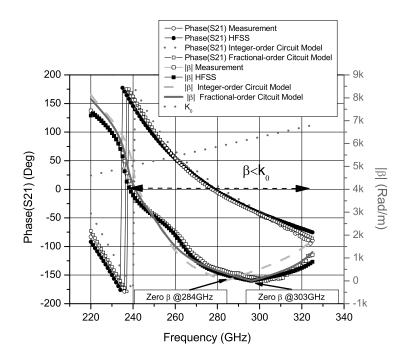

| 3.12 | Measurement, EM, integer-order and fractional-order circuits                                                                                                        | E            |

| 3.13 | simulation results: magnitude of S21 and S11 in dB<br>Measurement, EM, integer-order and fractional-order circuits                                                  | 5            |

| 3.13 | simulation results: phase of S21 in degree and the absolute                                                                                                         |              |

| 911  | value of extracted phase constant $\beta$                                                                                                                           | 5'           |

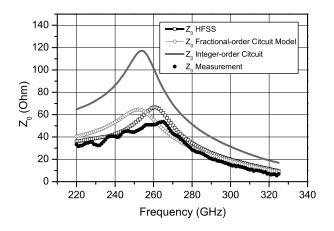

| 3.14 | Measurement, EM, integer-order and fractional-order circuits<br>simulation results: characteristic impedance of CRLH T-line                                         |              |

| 0.45 | $(\mathbf{Z}_0)$                                                                                                                                                    | $5^{\circ}$  |

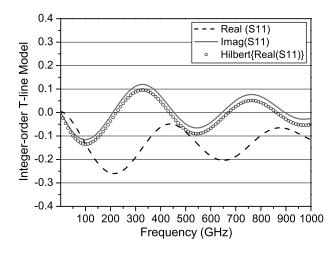

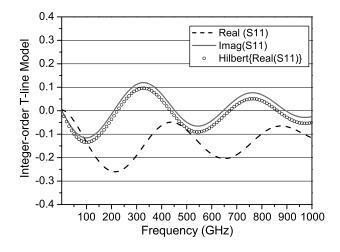

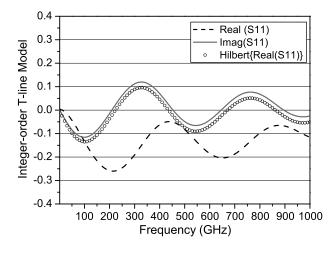

| 3.15 | Causality verification by Hilbert transformation: integer-order<br>T-line model S11.                                                                                | 5            |

| 3.16 | Causality verification by Hilbert transformation: fractional-<br>order T-line model S11                                                                                                 | 59 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.17 | Causality verification by Hilbert transformation: error magni-<br>tude comparison of S11.                                                                                               | 59 |

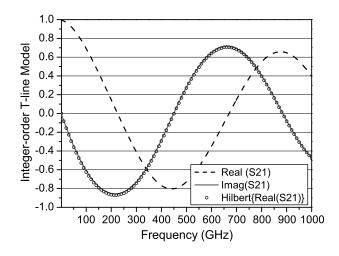

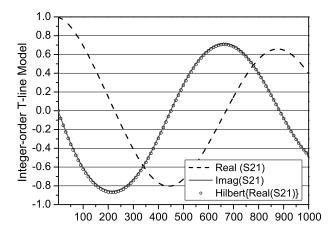

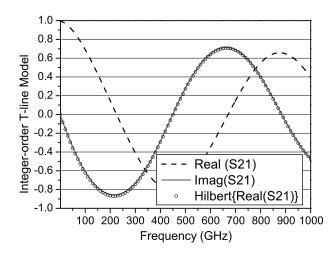

| 3.18 | Causality verification by Hilbert transformation: integer-order<br>T-line model S21.                                                                                                    | 60 |

| 3.19 | Causality verification by Hilbert transformation: fractional-<br>order T-line model S21.                                                                                                | 60 |

| 3.20 | Causality verification by Hilbert transformation: error magni-<br>tude comparison of S21.                                                                                               | 61 |

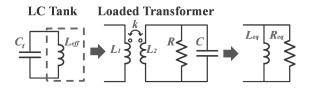

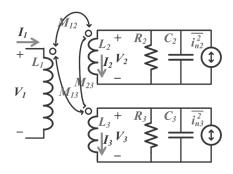

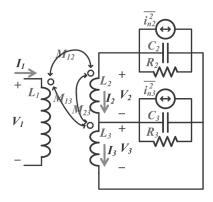

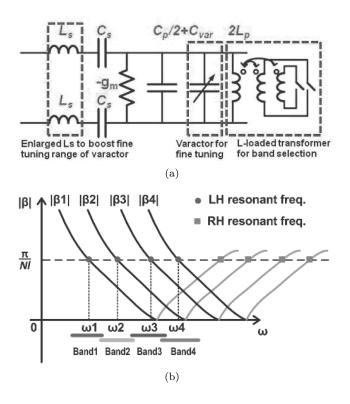

| 4.1  | Equivalent circuit model for inductive tuning of loaded trans-<br>former.                                                                                                               | 67 |

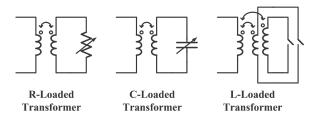

| 4.2  | Traditional resistor-, capacitor-, and inductor-loaded trans-<br>formers.                                                                                                               | 70 |

| 4.3  | Equivalent circuit model for conventional inductor-loaded transformer.                                                                                                                  | 70 |

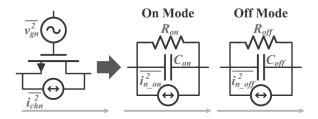

| 4.4  | Equivalent circuit model for switches                                                                                                                                                   | 71 |

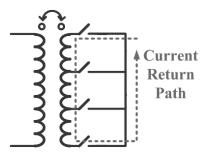

| 4.5  | Proposed new inductor-loaded transformer by switching cur-                                                                                                                              |    |

|      | rent return-paths with only one transformer                                                                                                                                             | 72 |

| 4.6  | Equivalent circuit model for the proposed loaded transformer.                                                                                                                           | 74 |

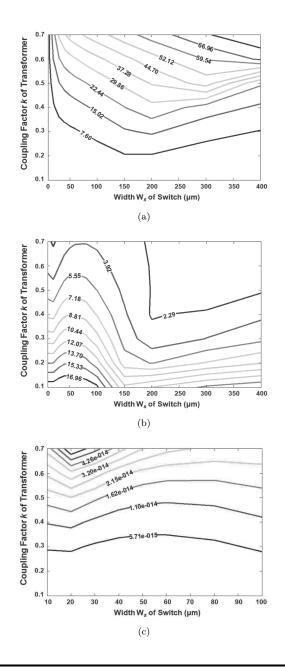

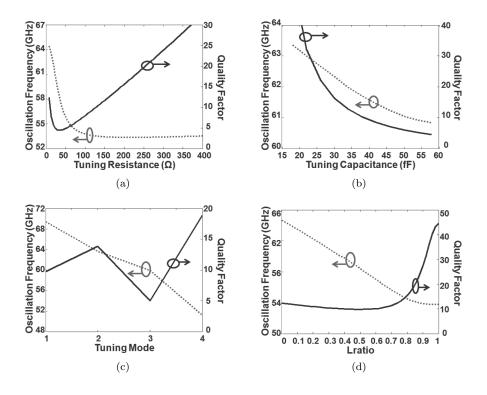

| 4.7  | Design optimization for (a) frequency tuning range (%), (b) the minimum quality factor in the tuning range, and (c) the maximum output noise spectral density at 10 MHz offset in       |    |

|      | tuning range.                                                                                                                                                                           | 75 |

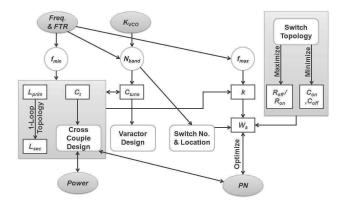

| 4.8  | Design optimization flow for wide-tuning VCO based on<br>the proposed inductor-loaded transformer, where performance<br>metrics are frequency, FTR, $K_{VCO}$ , power, and phase noise. | 76 |

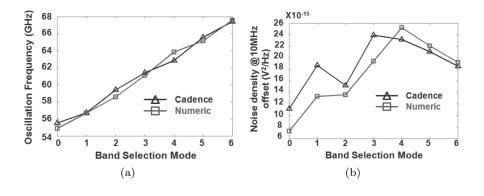

| 4.9  | Model validation: (a) oscillation frequency, (b) output noise density contributed by switches.                                                                                          | 77 |

| 4.10 | Numeric simulation for tuning range and quality factor of dif-<br>ferent loaded transformers.                                                                                           | 79 |

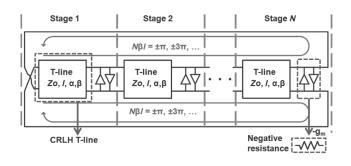

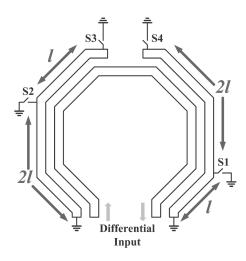

| 4.11 | CRLH T-line-based Mobius-ring RTW-VCO                                                                                                                                                   | 81 |

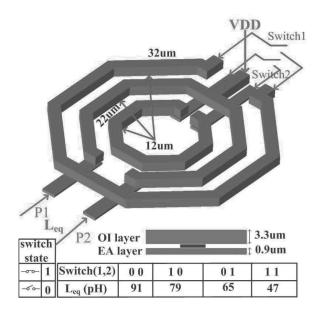

| 4.12 | Layout implementation for inductor-loaded transformer where                                                                                                                             | 01 |

|      | tuned inductance is determined by states of two switches                                                                                                                                | 83 |

| 4.13 | Tuning mechanism for the proposed tunable CRLH T-line-                                                                                                                                  |    |

|      | based Mobius-ring RTW-VCO.                                                                                                                                                              | 84 |

| 4.14 | Asymmetric layout implementation for the proposed new                                                                                                                                   |    |

|      | inductor-loaded transformer.                                                                                                                                                            | 86 |

| 4.15 | Schematic of the 60-GHz inductive-tuning VCO with asymmetric implementation of the proposed new inductor-loaded                                                                         |    |

|      | transformer.                                                                                                                                                                            | 87 |

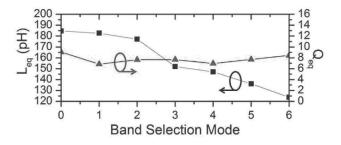

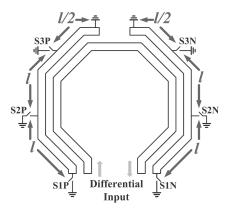

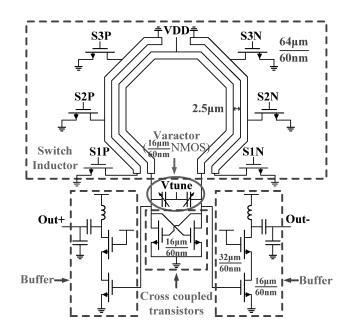

| 4.16 | Parameter extraction for the asymmetric loaded transformer design under various band selection modes                                                                                    | 88 |

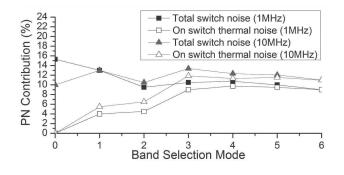

| 4.17           | Percentage of noise contribution from switches on asymmet-<br>ric loaded transformer implementation at 1 MH offset and 10<br>MHz offset. | 88         |

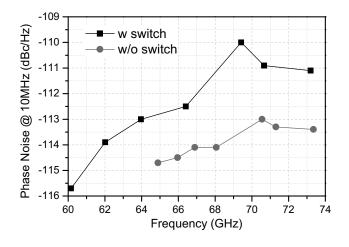

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.18           | Simulation comparison for VCO performance (phase noise and oscillation frequency) with and without switches.                             | 89         |

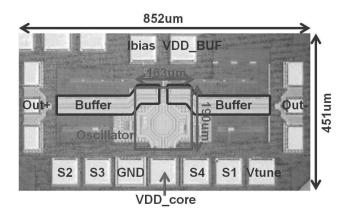

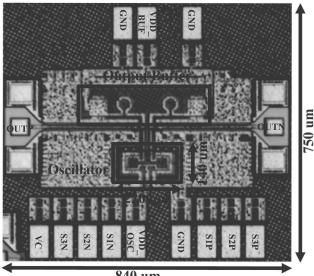

| 4.19           | Die photo for the 60-GHz asymmetric VCO with fabricated in STM 65 nm CMOS technology.                                                    | 90         |

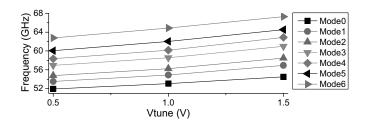

| 4.20           | Measured tuning curves under different band selection modes<br>for the 60-GHz asymmetric VCO                                             | 91         |

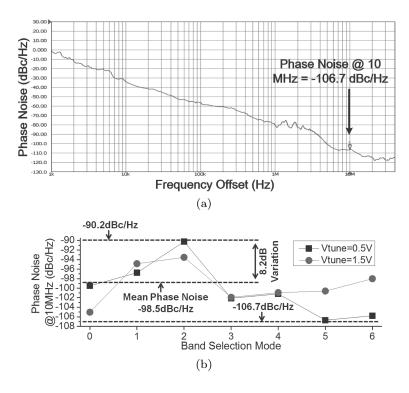

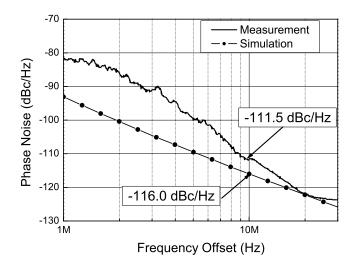

| 4.21           | Measured phase noise performance for the 60-GHz asymmetric VCO                                                                           | 92         |

| 4.22           | Symmetric layout implementation for the proposed new inductor-loaded transformer.                                                        | 93         |

| 4.23           | Schematic of the 60-GHz inductive-tuning VCO with symmetric implementation of the proposed new inductor-loaded                           |            |

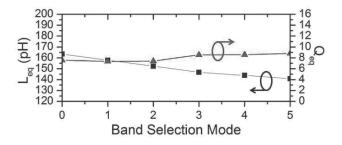

| 4.24           | transformer                                                                                                                              | 94         |

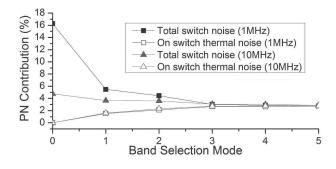

| 4.25           | design under various band selection modes Percentage of noise contribution from switches on symmetric                                    | 96         |

| 4.90           | loaded transformer implementation at 1 MHz offset and 10 MHz offset.                                                                     | 97         |

| 4.26           | Die photo for the 60-GHz symmetric VCO fabricated in Global<br>Foundries 65 nm CMOS technology.                                          | 98         |

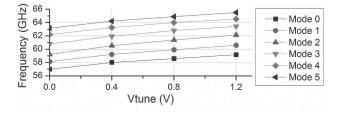

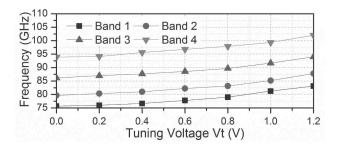

| 4.27           | Measured tuning curves under different band selection modes<br>for the 60-GHz symmetric VCO                                              | 98         |

| 4.28           | Measured phase noise performance for the 60-GHz symmetric VCO.                                                                           | 99         |

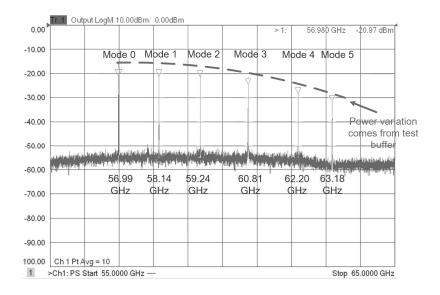

| 4.29           | Measured output spectrum of equally spaced starting frequencies under 6 different modes for the 60-GHz symmetric VCO.                    | 100        |

| 4.30           | (a) Die micrograph of the proposed VCO. (b) The EM simulation for one CRLH T-line unit-cell.                                             | 101        |

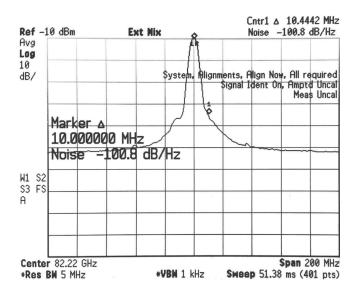

| $4.31 \\ 4.32$ | Measured frequency tuning range by 4 sub-bands Measured phase noise at 82.22 GHz with 10 MHz offset fre-                                 | 101        |

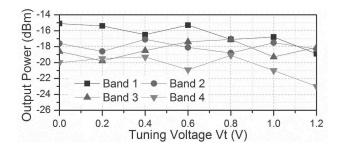

| 4.33           | quency                                                                                                                                   | 102<br>103 |

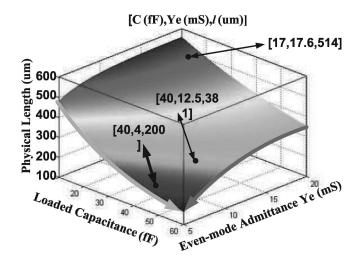

| 5.1            | (a) Equivalent circuit of differential ZPC loaded with parasitic capacitance; (b) on-chip realization of inter-digital coupled T-        |            |

| 5.2            | lines                                                                                                                                    | 107        |

| 5.3            | and even-mode characteristic admittance at 60 GHz<br>Layout of inter-digital differential ZPC with effective electrical                  | 109        |

|                | length controlled by MOS switches                                                                                                        | 110        |

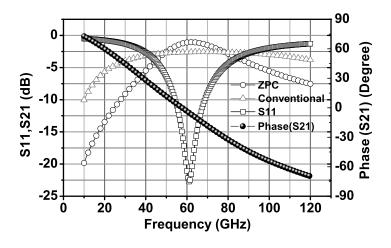

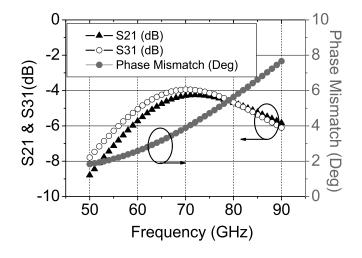

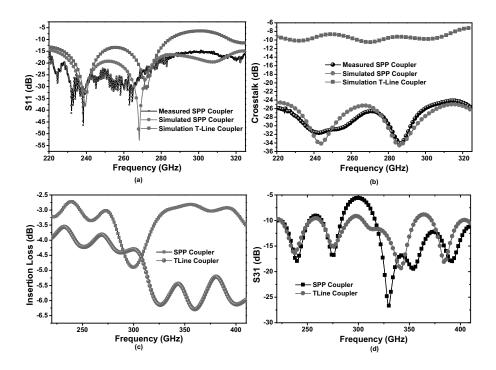

| 5.4  | Simulated magnitude of S11 and S21 in dB and phase of S21 of<br>the proposed coupler structure with comparison of S21 mag- |     |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

|      | nitude to the conventional one by coupled T-line.                                                                          | 110 |

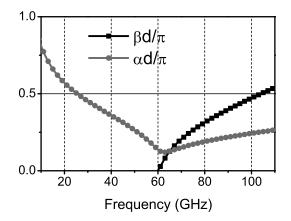

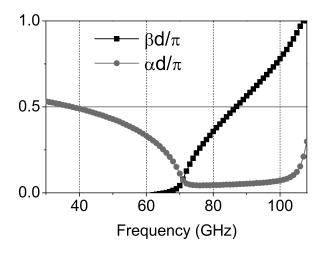

| 5.5  | The extracted dispersion diagram and relative permittivity                                                                 |     |

|      | $(\varepsilon_r)$ .                                                                                                        | 111 |

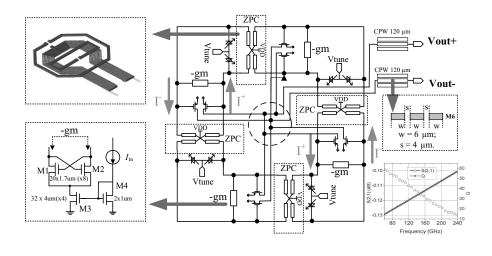

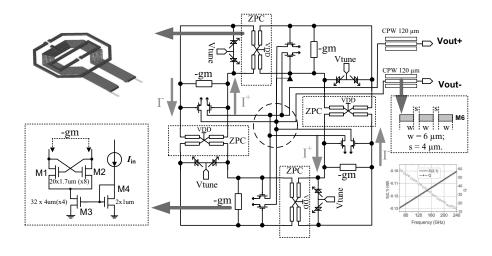

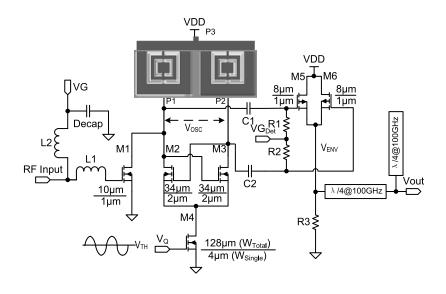

| 5.6  | Schematic of proposed VCO with differential outputs com-                                                                   |     |

|      | bined at the center.                                                                                                       | 112 |

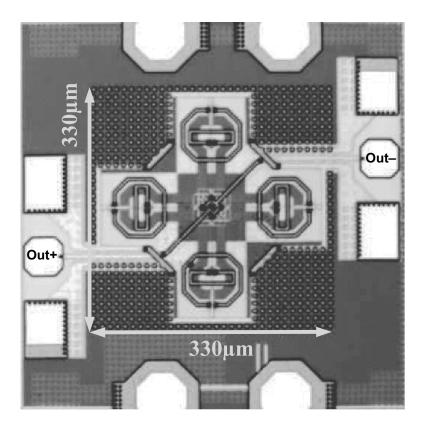

| 5.7  | Die micrograph of the fabricated 60 GHz VCO chip in 65 nm                                                                  |     |

|      | CMOS.                                                                                                                      | 113 |

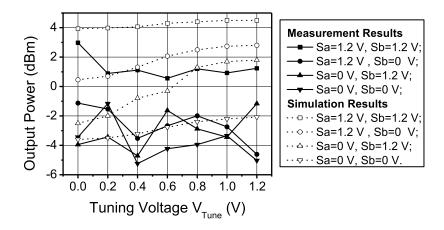

| 5.8  | Measured and simulated output power and power efficiency of                                                                |     |

|      | proposed VCO over entire 60 GHz band.                                                                                      | 114 |

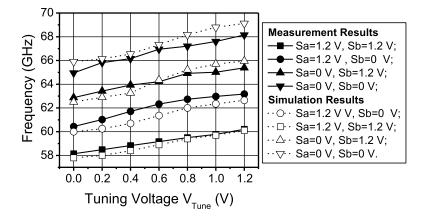

| 5.9  | Measured and simulated VCO FTR under various switch con-                                                                   |     |

|      | figurations to cover 58.3–64.8 GHz continuously                                                                            | 115 |

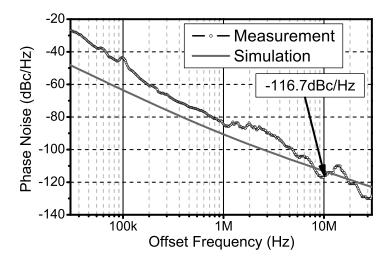

| 5.10 | Measured and simulated VCO phase noise at 60 GHz                                                                           | 115 |

| 5.11 | Block diagram of proposed 140 GHz signal source with center                                                                |     |

|      | combined output from four 70 GHz zero-phase-coupled oscil-                                                                 |     |

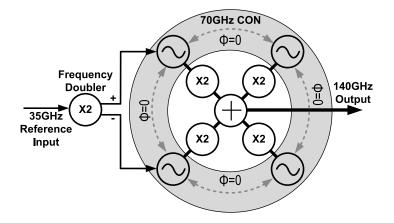

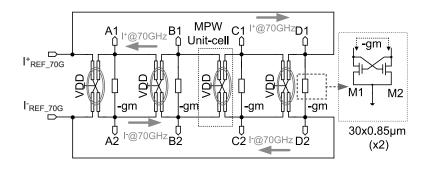

|      | lator unit-cells.                                                                                                          | 117 |

| 5.12 | Schematic of on-chip ZPC-based oscillator unit-cell at 70-GHz                                                              |     |

|      | band with inter-digital coupled T-line and switch-controlled                                                               |     |

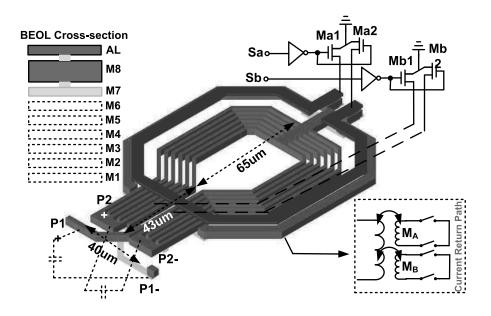

|      | inductive loadings.                                                                                                        | 118 |

| 5.13 | EM simulation results of 70-GHz ZPC with inter-digital cou-                                                                |     |

|      | pled T-line.                                                                                                               | 119 |

| 5.14 | Extracted dispersion diagram of 70 GHz ZPC with inter-                                                                     |     |

|      | digital coupled T-line                                                                                                     | 119 |

| 5.15 | Schematic of injection-locked 70-GHz CON with 4 oscillator                                                                 |     |

|      | unit-cells                                                                                                                 | 120 |

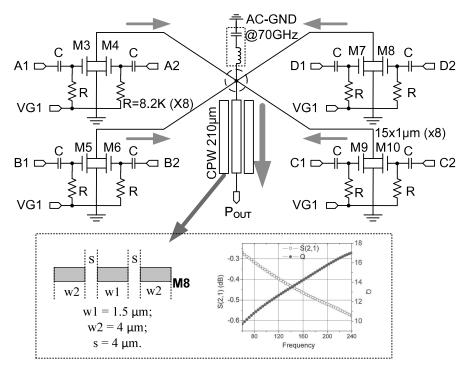

| 5.16 | Schematic of four 70-GHz to 140-GHz push-push frequency                                                                    |     |

|      | doublers with center combined output.                                                                                      | 120 |

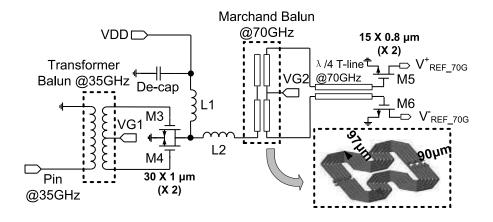

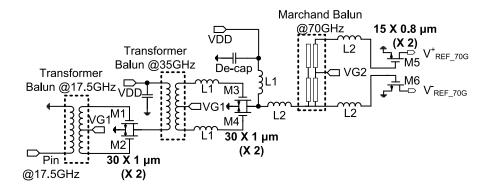

| 5.17 | Schematic of 35 GHz to 70 GHz frequency doubler with inter-                                                                |     |

|      | digital Marchand balun at 70 GHz                                                                                           | 121 |

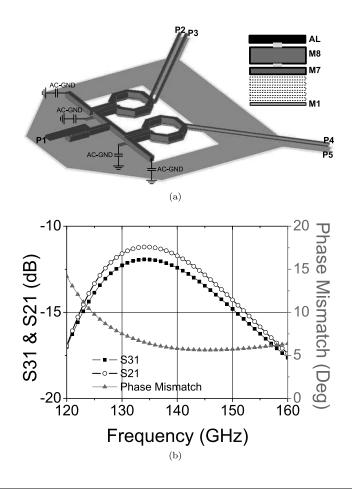

| 5.18 | EM simulation results of the proposed Marchand balun at 70                                                                 |     |

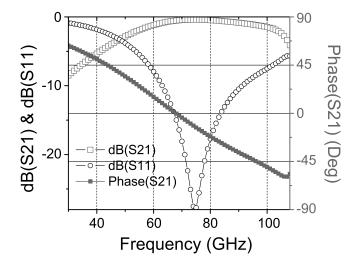

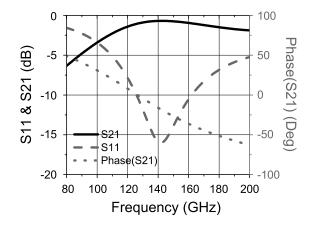

|      | GHz                                                                                                                        | 122 |

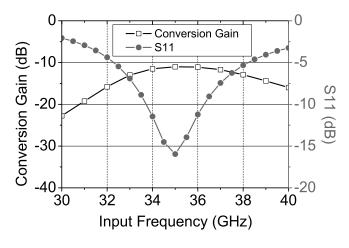

| 5.19 | Post-layout simulation results of the 35-GHz to 70-GHz fre-                                                                |     |

|      | quency doubler.                                                                                                            | 122 |

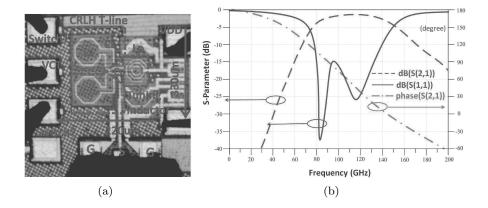

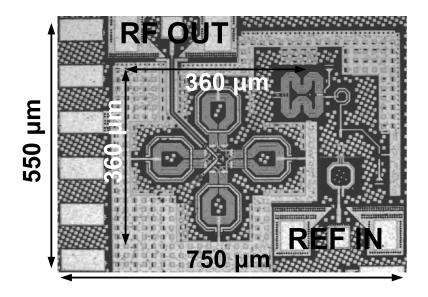

| 5.20 | Die micrograph of the fabricated THz source in CMOS                                                                        | 123 |

| 5.21 | Measured and simulated output power of signal source with                                                                  |     |

|      | three different inductive loading modes                                                                                    | 123 |

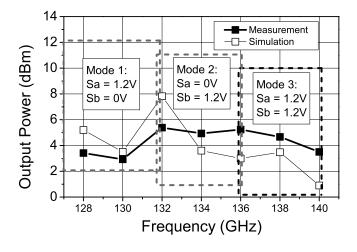

| 5.22 | Measured and simulated output spectrum of the proposed sig-                                                                |     |

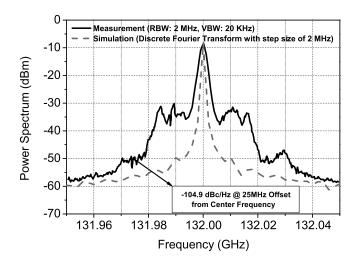

|      | nal source at 132 GHz                                                                                                      | 124 |

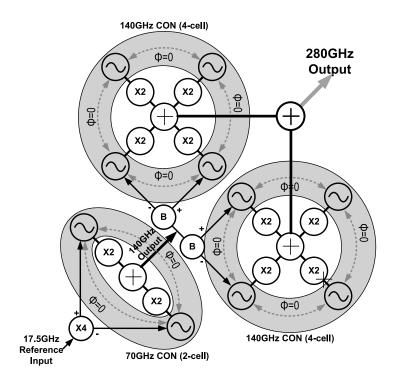

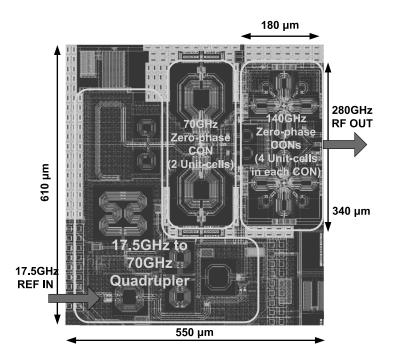

| 5.23 | Block diagram of proposed 280 GHz signal source                                                                            | 126 |

| 5.24 | Schematic of on-chip MPW base oscillator unit-cell at 140-                                                                 |     |

|      | GHz band with inter-digital coupled T-line                                                                                 | 127 |

| 5.25 | EM simulation results of 140-GHz on-chip MPW unit-cell with                                                                |     |

|      | inter-digital coupled T-line                                                                                               | 127 |

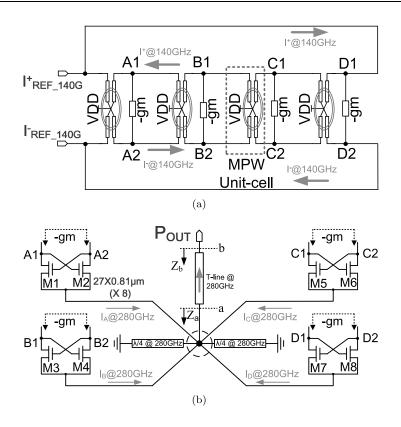

| 5.26           | (a) Schematic of injection-locked 140 GHz CON with 4 MPW unit-cells; (b) 2nd harmonic outputs power combining net- |              |

|----------------|--------------------------------------------------------------------------------------------------------------------|--------------|

| 5.27           | work                                                                                                               | 128          |

|                | cells.                                                                                                             | 129          |

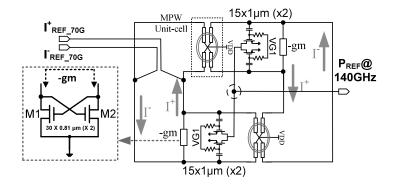

| 5.28           | 140 GHz power splitter from one single-ended input to two differential outputs.                                    | 130          |

| 5.29           | Input reference frequency quadrupler from 17.5 GHz to 70 GHz.                                                      | 131          |

| 5.30           | Post-layout simulation results of 17.5 GHz to 70 GHz quadrupler.                                                   | 131          |

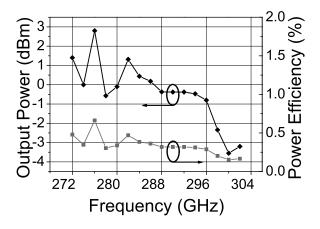

| $5.31 \\ 5.32$ | Cadence layout of the proposed 280 GHz source in CMOS<br>Simulated output power of the proposed 280 GHz source in  | $131 \\ 132$ |

| 0.02           | CMOS.                                                                                                              | 132          |

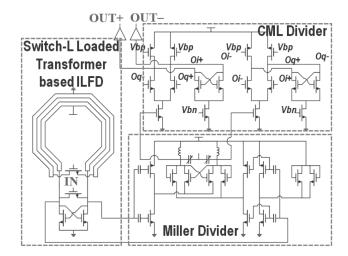

| 6.1            | Schematic of designed CMOS 60-GHz PLL.                                                                             | 136          |

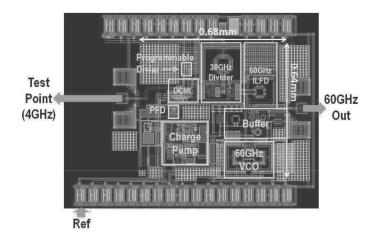

| 6.2            | Layout of designed CMOS 60-GHz PLL.                                                                                | 136          |

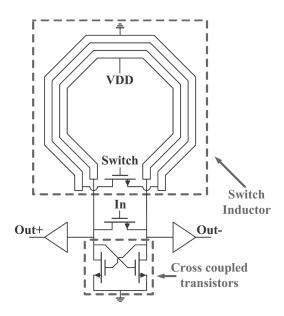

| 6.3            | Schematic of switch-inductor loaded transformer-based ILFD.                                                        | 138          |

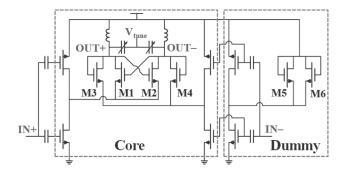

| 6.4            | Schematic of the 30-GHz ILFD.                                                                                      | 139          |

| 6.5            | Schematic of the 60-GHz divider chain                                                                              | 139          |

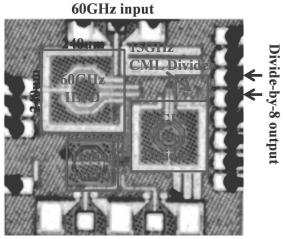

| 6.6            | Chip micrography of 60-GHz PLL in Global Foundries 65 nm                                                           |              |

|                | technology                                                                                                         | 140          |

| 6.7            | 60-GHz divider chain die photo.                                                                                    | 141          |

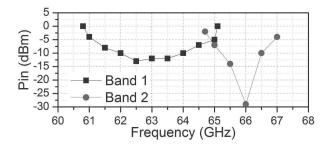

| 6.8            | Measured sensitivity curve of the 60-GHz ILFD                                                                      | 141          |

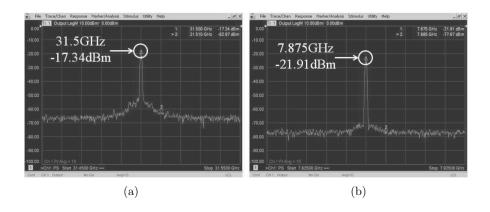

| 6.9            | Measured divide-by-2 and divide-by-8 output spectrums at                                                           |              |

|                | 63-GHz input signal.                                                                                               | 142          |

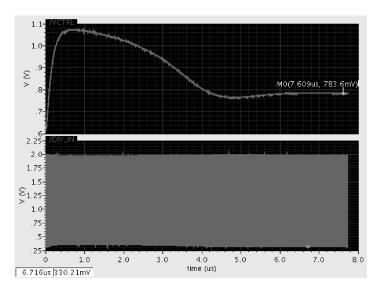

| 6.10           | Simulated locking process of designed 60-GHz PLL at 62.64 GHz.                                                     | 142          |

| 7.1            | Proposed 2D active CRLH T-line network                                                                             | 149          |

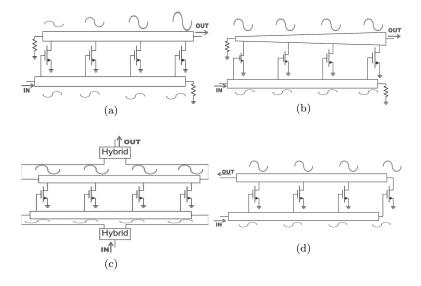

| 7.2            | Distributed amplifier (DA) topologies: (a) conventional DA,<br>(b) tapered DA, (c) DFDA, (d) SEDFDA.               | 151          |

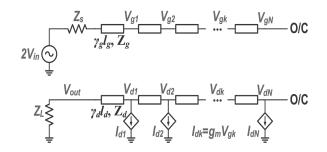

| 7.3            | Equivalent circuit for single-ended dual-fed distributed ampli-                                                    | 151          |

| 1.5            | fier (SEDFDA).                                                                                                     | 152          |

| 7.4            | Effect of T-line loss on SEDFDA performance.                                                                       | 152          |

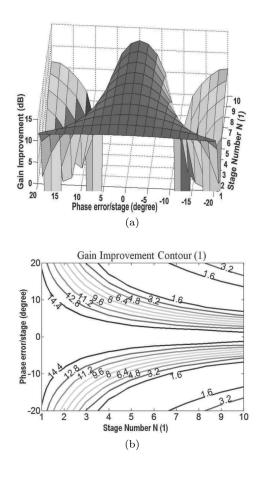

| 7.5            | Effect of T-line phase error on SEDFDA performance: (a) 3D                                                         | 104          |

| 1.0            | diagram, (b) contour diagram.                                                                                      | 156          |

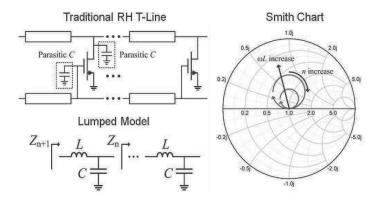

| 7.6            | Traditional right-handed T-line analysis.                                                                          | 158          |

| 7.7            | Zero-phase CRLH T-line analysis: lumped model and Smith                                                            | 100          |

|                | chart                                                                                                              | 158          |

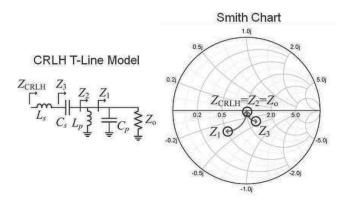

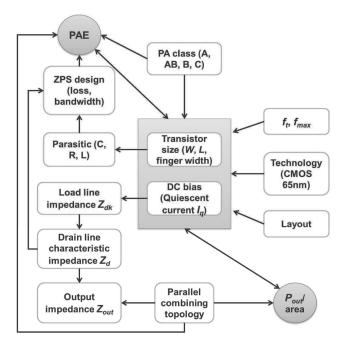

| 7.8            | Design consideration for the proposed 2D distributed power                                                         | 100          |

|                | combining network.                                                                                                 | 159          |

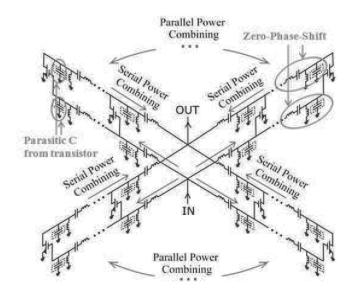

| 7.9            | Differential version of proposed SEDFDA PA topology based                                                          | -00          |

|                | on 2D distributed power combining network with the use of                                                          |              |

|                | CRLH ZPSs                                                                                                          | 161          |

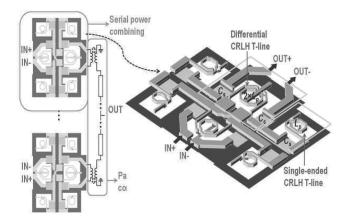

| 7.10 | The proposed layout for differential 2D power combining net-                          | 169  |

|------|---------------------------------------------------------------------------------------|------|

| 711  | work.                                                                                 | 162  |

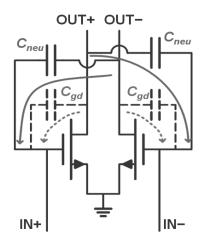

| 7.11 | Neutralization technique for PA stabilization.                                        | 163  |

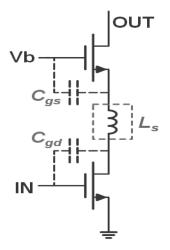

| 7.12 | Cascode topology for PA stabilization.                                                | 164  |

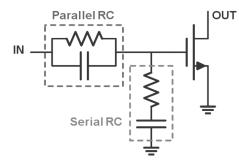

| 7.13 | RC networks for PA stabilization.                                                     | 165  |

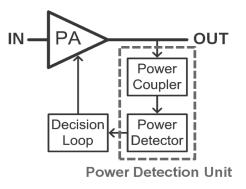

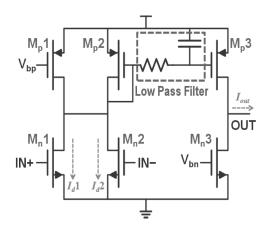

| 7.14 | Power detection unit.                                                                 | 168  |

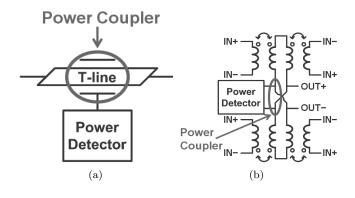

| 7.15 | Power coupler topologies: (a) capacitive coupling from output;                        | 1.00 |

|      | (b) direct connection from output                                                     | 168  |

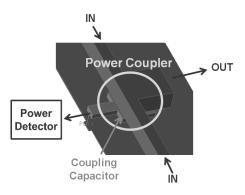

| 7.16 | Designed capacitive power coupler                                                     | 169  |

| 7.17 | Square-law power detector                                                             | 170  |

| 7.18 | Designed single-ended square low power detector                                       | 171  |

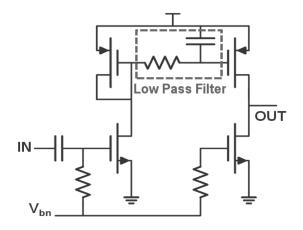

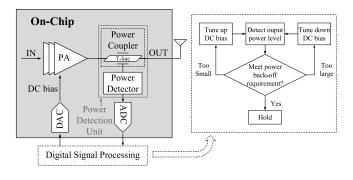

| 7.19 | Designed digital control system                                                       | 171  |

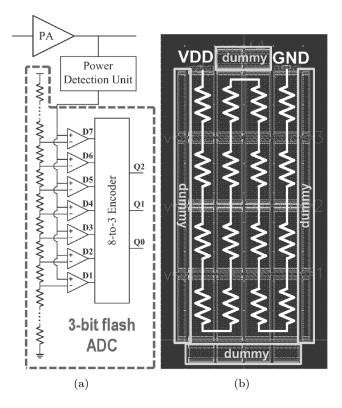

| 7.20 | ADC design: (a) flash ADC topology; (b) resistor array to                             |      |

|      | generate reference voltage                                                            | 172  |

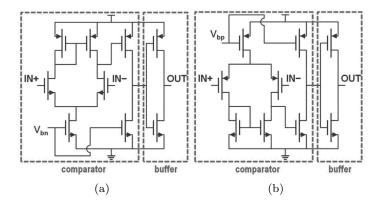

| 7.21 | Comparator topologies for ADC design: (a) n-type; (b) p-type.                         | 173  |

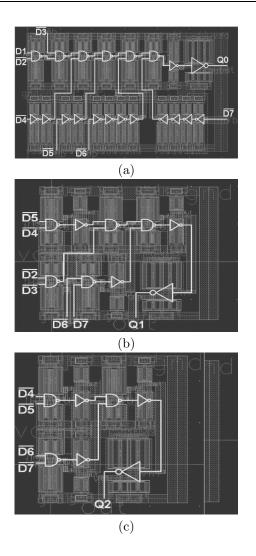

| 7.22 | 8-to-3 encoder for ADC design: (a) Q0, (b) Q1, (c) Q2                                 | 174  |

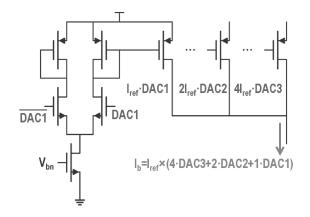

| 7.23 | DAC topology.                                                                         | 175  |

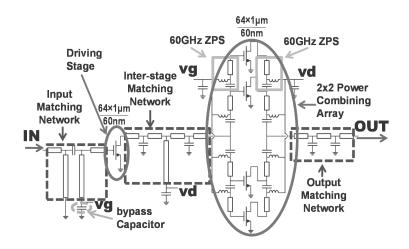

| 7.24 | Schematic of 2-stage PA with a $2 \times 2$ distributed power com-                    |      |

|      | bining network.                                                                       | 175  |

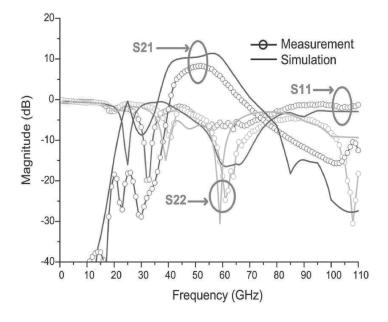

| 7.25 | Simulated and measured S parameters of PA under 1.2 V sup-                            |      |

|      | ply                                                                                   | 176  |

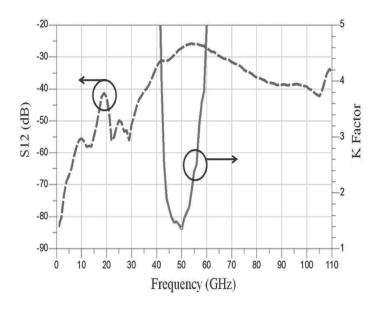

| 7.26 | Reverse isolation and stability of PA under 1.2 V supply                              | 177  |

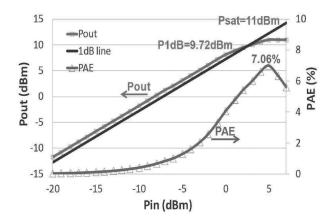

| 7.27 | Measured power and PAE of PA at 52 GHz under $1.2$ V                                  |      |

|      | supply                                                                                | 178  |

| 7.28 | Die micrograph with block illustrations.                                              | 179  |

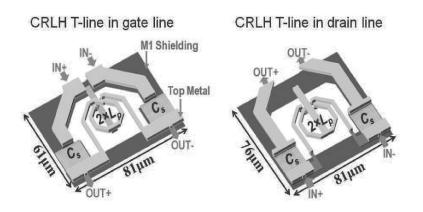

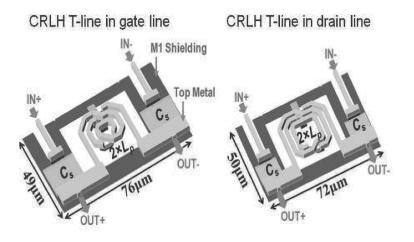

| 7.29 | On-chip implementation of CRLH T-line (metamaterial) to                               |      |

|      | realize zero-phase shift in standard CMOS technology for the                          |      |

|      | 60 GHz PA prototype with differential $2 \times 4$ distributed power                  |      |

|      | combining network                                                                     | 180  |

| 7.30 | Schematic of 3-stage differential PA with differential $2 \times 4$ dis-              |      |

|      | tributed power combining network                                                      | 181  |

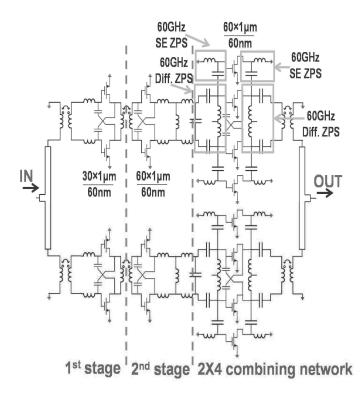

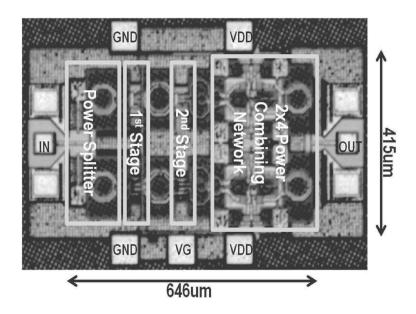

| 7.31 | Die micrograph of PA with 2D power combining network by                               |      |

|      | zero-phase-shifter.                                                                   | 182  |

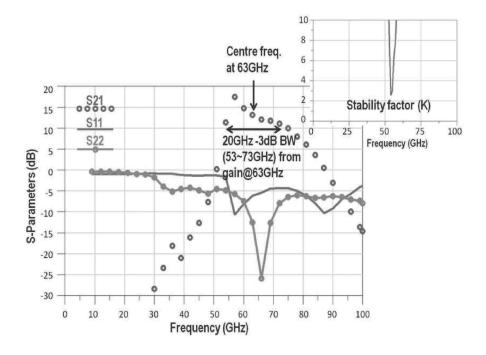

| 7.32 | The measured S parameters of PA and its stability factor with                         |      |

|      | center frequency (63 GHz) under 1 V supply                                            | 183  |

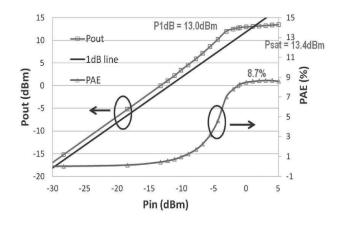

| 7.33 | The measured output power and PAE of PA at center fre-                                |      |

|      | quency (63 GHz) under 1 V supply                                                      | 184  |

| 7.34 | On-chip implementation of CRLH T-line (metamaterial) to                               |      |

|      | realize zero-phase shift in standard CMOS technology for the                          |      |

|      | 60  GHz PA prototype with differential 4×4 distributed power                          |      |

|      | combining network.                                                                    | 184  |

| 7.35 | EM simulation results of both loaded CRLH T-line and loaded                           | 104  |

| 1.00 | $\lambda/2$ T-line for comparison                                                     | 185  |

|      | $n_{\mu}$ = mo tor companson, $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ | 100  |

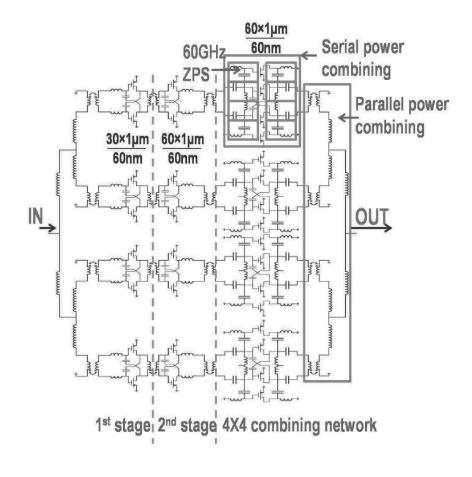

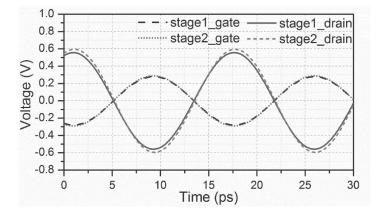

| 7.36 | Schematic of the 60-GHz PA prototype with 3 stages and differential $4\times 4$ distributed power combining network at $3^{rd}$                                                                          |                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

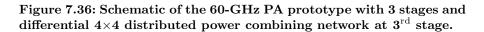

| 7.37 | stage                                                                                                                                                                                                    | 186                                       |

| - 00 | biner.                                                                                                                                                                                                   | 187                                       |

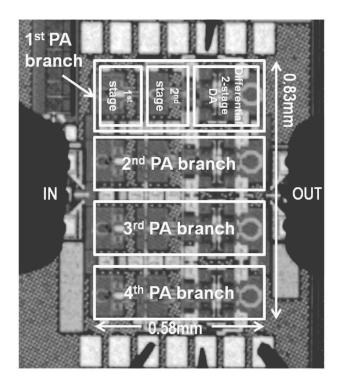

| 7.38 | Die micrograph of the 60 GHz PA prototype with differential $4 \times 4$ distributed power combining network.                                                                                            | 188                                       |

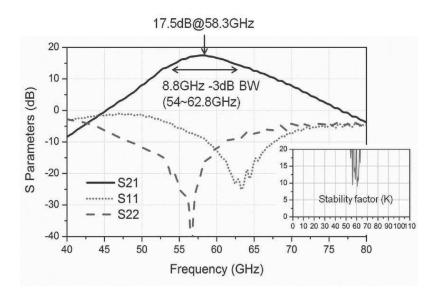

| 7.39 | The measured S parameters of the PA prototype and its sta-                                                                                                                                               |                                           |

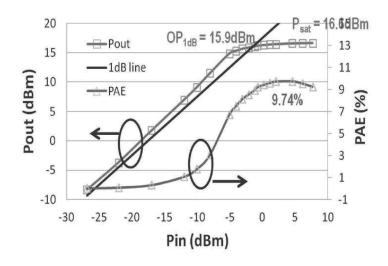

| 7.40 | bility factor under 1.2 V supply                                                                                                                                                                         | 189                                       |

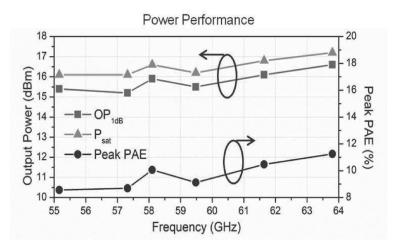

|      | center frequency (58.3 GHz) under 1.2-V supply                                                                                                                                                           | 190                                       |

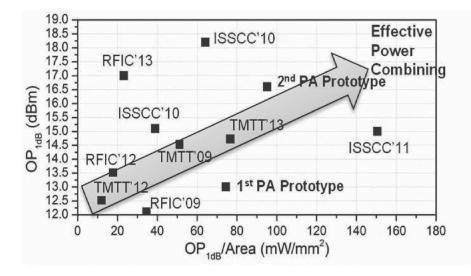

| 7.41 | Measured power performance of the PA prototype over 60-GHz band (57 ~ 64 GHz), where >15 dBm $OP_{1dB}$ and >16 dBm $P_{sat}$ are observed with peak values of 16.6 dBm and 17.2                         |                                           |

| 7.42 | dBm, respectively                                                                                                                                                                                        | 190                                       |

| 7.43 | bining networks with state-of-the-art 60-GHz CMOS PAs DAC control of PA output power and improved efficiency dur-                                                                                        | 191                                       |

|      | ing power back-off.                                                                                                                                                                                      | 193                                       |

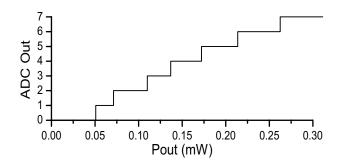

| 7.44 | ADC outputs for PA output power detection at 58.3 GHz.                                                                                                                                                   | 194                                       |

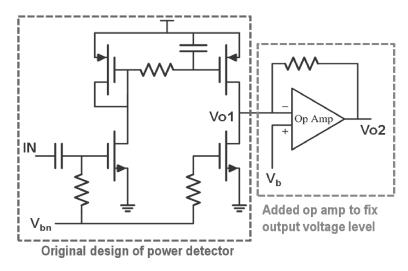

| 7.45 | Modification for the power detector design                                                                                                                                                               | 194                                       |

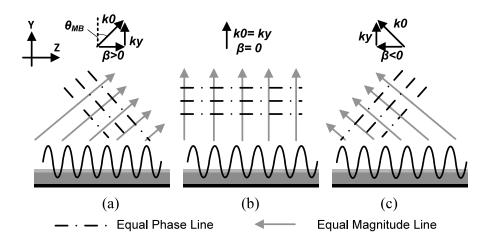

| 8.1  | Operation diagram of leaky wave antenna: (a) $\beta > 0$ , (b)                                                                                                                                           |                                           |

|      | $\beta = 0$ , and (c) $\beta < 0$                                                                                                                                                                        | 199                                       |

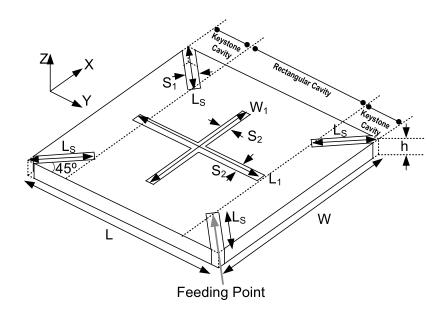

| 8.2  | Geometrical configuration of the proposed SIW antenna with                                                                                                                                               | 200                                       |

| 8.3  | four corner slots                                                                                                                                                                                        | 200                                       |

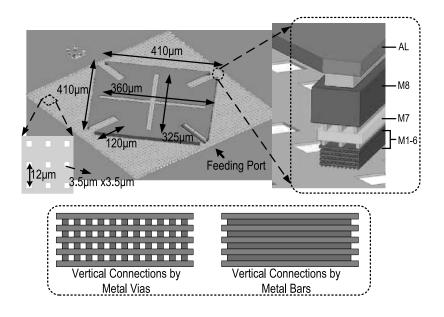

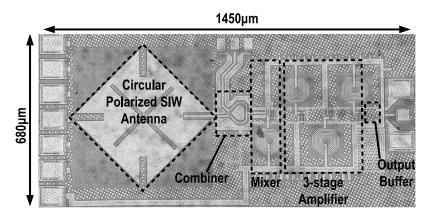

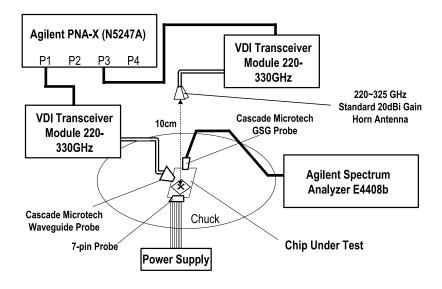

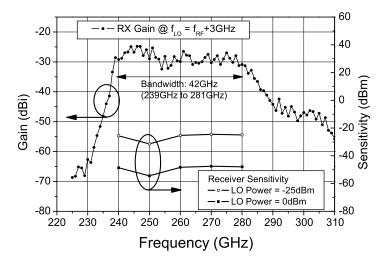

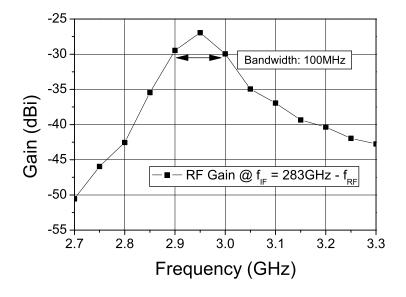

| 8.4  | in CMOS 65 nm process                                                                                                                                                                                    | $\begin{array}{c} 202 \\ 203 \end{array}$ |

| 8.5  | Structure of CRLH T-line-based 2D phase-arrayed array in                                                                                                                                                 | 200                                       |

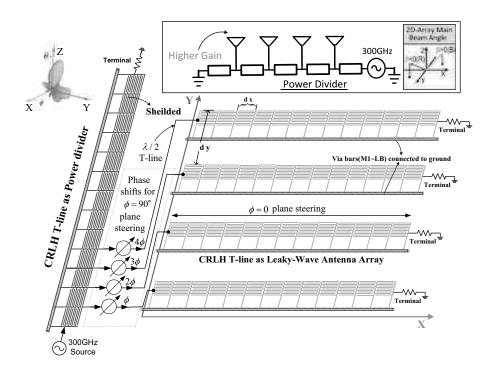

|      | THz                                                                                                                                                                                                      | 204                                       |

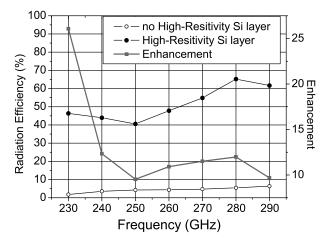

| 8.6  | Radiation efficiency enhancement by stacking a high-                                                                                                                                                     |                                           |

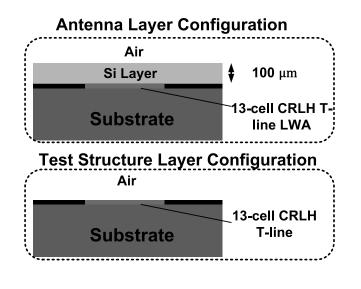

|      | resistivity Si layer                                                                                                                                                                                     | 204                                       |

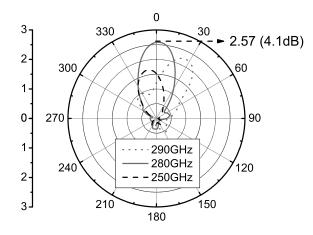

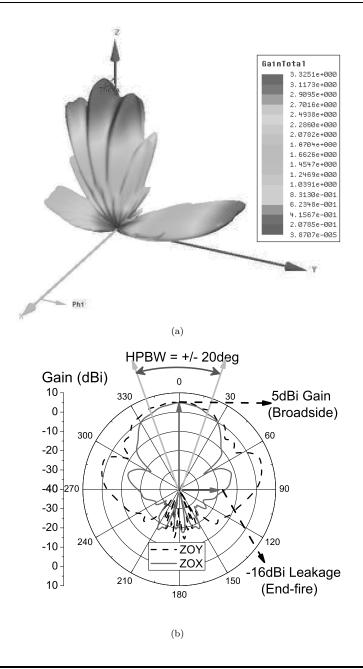

| 8.7  | Gain radiation patterns for the proposed 1D LWA array at                                                                                                                                                 |                                           |

|      | three frequencies: $f = 250 \text{ GHz} (\beta < 0, \text{ backward radiation}),$                                                                                                                        |                                           |

|      | $f = 280 \text{ GHz} \ (\beta = 0, \text{ broadside radiation}), \text{ and } f = 290 \text{ GHz} \ (\beta > 0, \text{ forward radiation}). \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 205                                       |

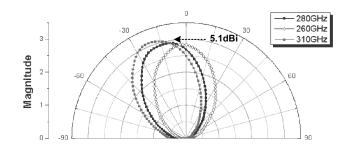

| 8.8  | Gain radiation patterns for the proposed 2D LWA array at three frequencies: $f = 260$ GHz, $f = 280$ GHz and $f =$                                                                                       | 205                                       |

|      | 310 GHz                                                                                                                                                                                                  | 205                                       |

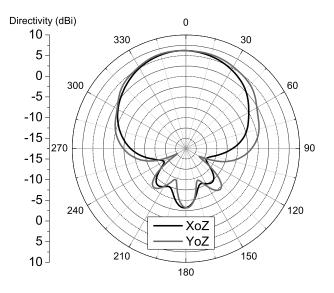

| 8.9  | HFSS simulation results of proposed SIW antenna directivity at 270 GHz.                                                                                                                                  | 206                                       |

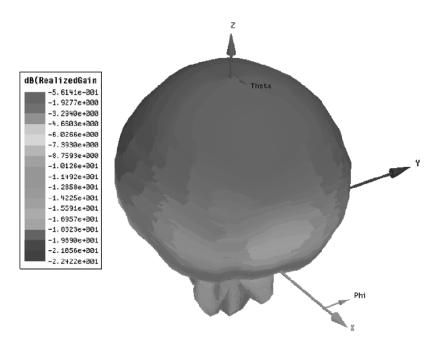

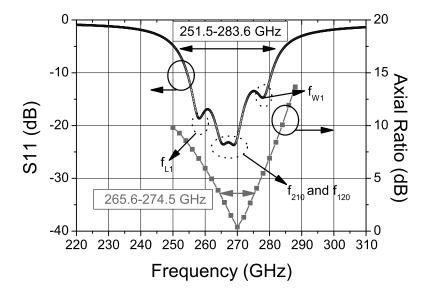

| HFSS simulation results of the proposed SIW antenna radia-<br>tion pattern at 270 GHz.                                    | 207                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

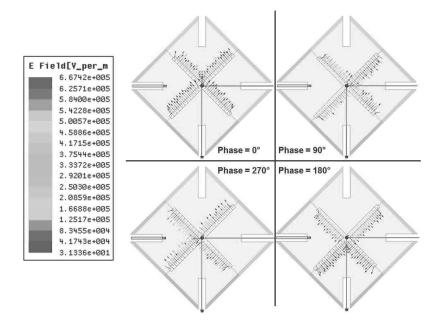

| HFSS simulation results of polarized vector electric field in the                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                           | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| on broadside radiation direction.                                                                                         | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

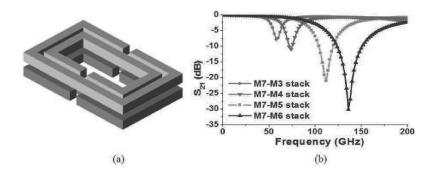

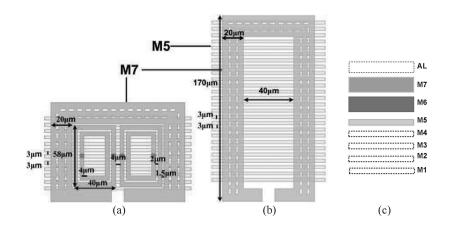

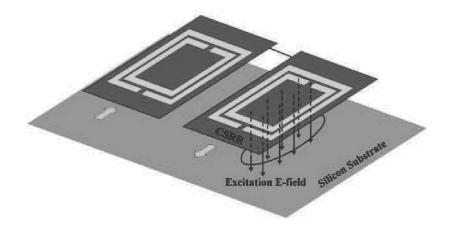

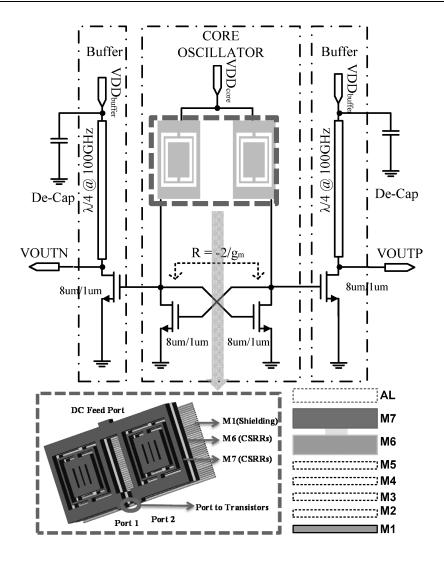

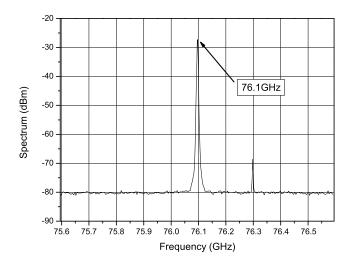

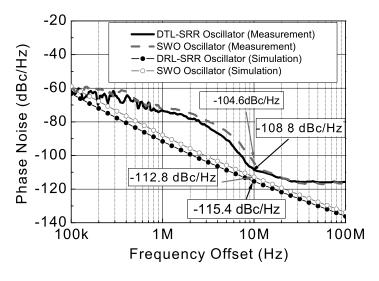

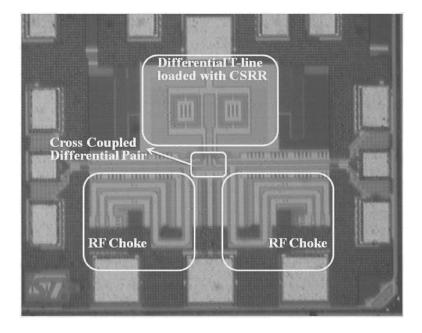

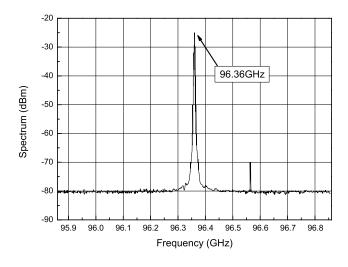

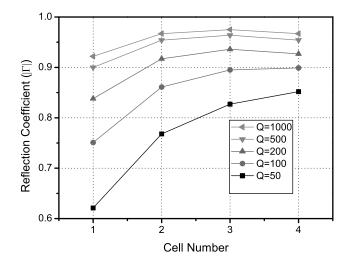

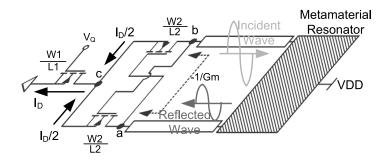

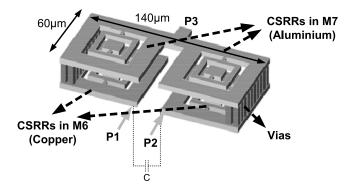

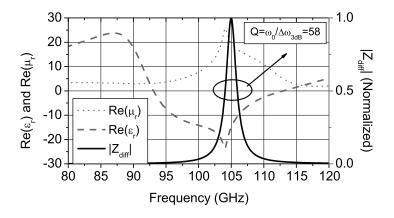

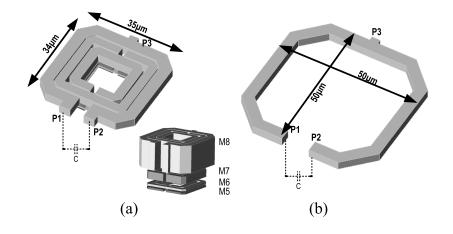

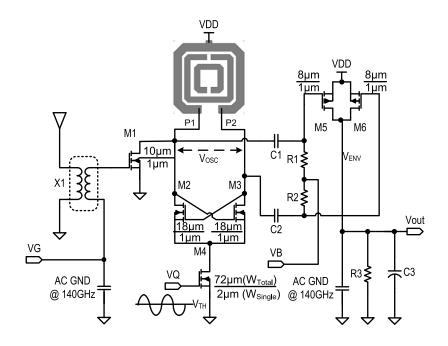

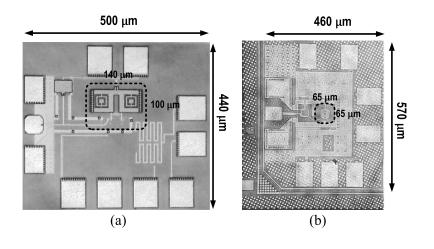

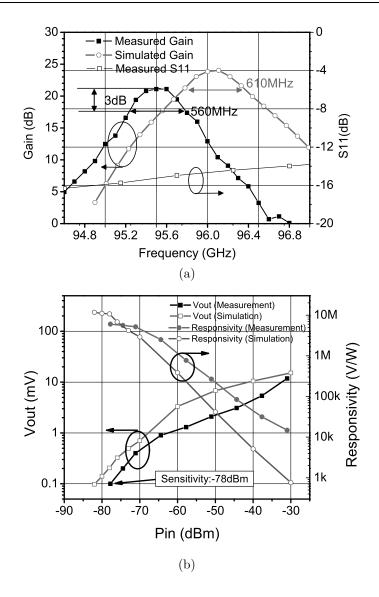

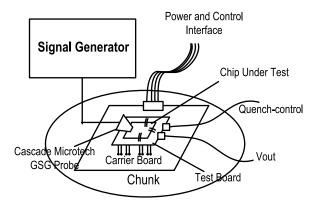

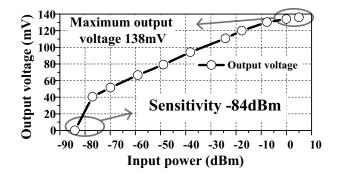

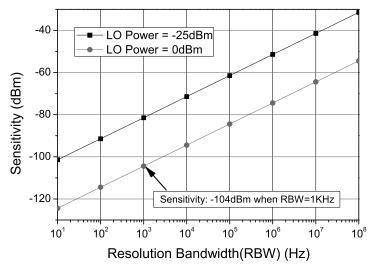

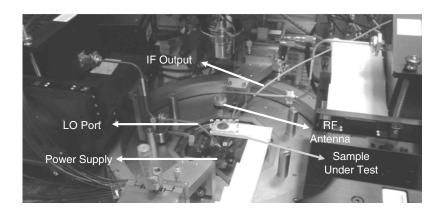

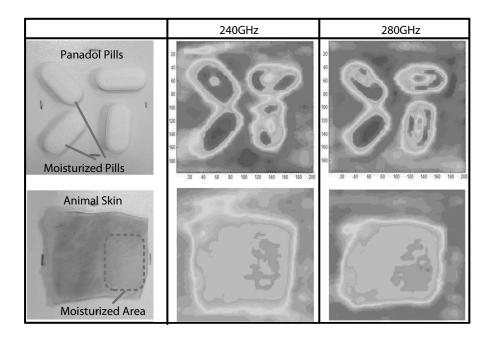

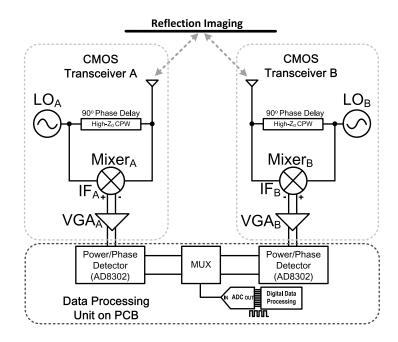

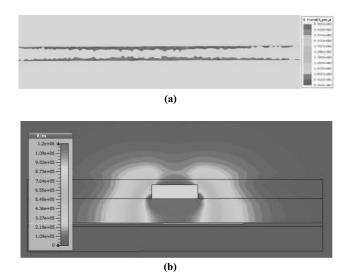

| (a) Stacked SRR unit-cell designed by metal layers of M7 and M6; (b) S21 simulation results with different stacking meth- | 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |